(二)DDR协议基础进阶——(Pinout信号组成、地址关系)_ddr信号-程序员宅基地

技术标签: fpga开发 硬件工程 DDR协议及应用实践 驱动开发

文章目录

一、DDR的信号分析

DDR在完整的PC端或移动电子消费端中属于芯片的外挂组件,其引脚信号按照功能可以分为6大类:前3类为时钟信号、地址及控制信号、数据信号;后3类为电源信号、接地信号、配置信号。

下面以DDR3为例,其具体的信号信息如下表:(带#的信号表示低电平有效信号)

| 分类 | 信号名 | 方向 | 源 | 描述 |

|---|---|---|---|---|

| 时钟复位及片选信号 | CK,CK# | IN | 系统时钟差分信号,上升沿/下降沿 | 差分时钟信号,由DDR Controller输出。所有地址和控制信号在CK#下降沿和CK的上升沿的交叉点被采样,数据选通(DQS# / DQS)参考交叉点 |

| CKE, (CKE0), (CKE1) | IN | 时钟使能 | CLock enable,主要应用于低功耗模式;一般情况下为高,只有当DDR进入的power_down或者自刷新模式下时,CKE信号才会拉低。 | |

| CS#,(CS0#), (CS1#), (CS2#), (CS3#) | IN | Rank片选使能 | Chip Select, CS#低有效,当该信号为高时,所有命令都会被masked(无效),该信号主要用于多个RANK时的RANK组选择;一个Rank通常由多个DDR颗粒组成,由于这些颗粒复用同一个CS#信号,因此属于一片Rank | |

| ODT, (ODT0), (ODT1) | IN | 阻抗匹配使能 | ON-Die Termination,具体指在数据通道上对DDR颗粒内部的终端匹配电阻进行打开(使能)的信号:ODT信号可使能DDR3 SDRAM内部的RTT_NOM终端电阻。在x4/x8配置中,ODT仅对每个DQ、DQS、DQS#以及DM/TDQS、NU/TDQS#有用。在x16配置中,ODT仅对每个DQ、DQSU、DQSU#、DQSL、DQSL#、DMU以及DML有用。当MR1寄存器中禁止RTT_NOM时,ODT信号将不起作用 | |

| RESET_n | IN | 复位信号 | DDR复位信号,低电平有效。正常操作过程中,保持高电平,主要用来复位memory内部的寄存器 |

- CKE与CS#信号是一一对应的,当DDR SDRAM有多片Rank时,也就意味着存在多个CS#和CKE;例如当有2片Rank时,则必然存在CS0#和CS1#与之对应,同样存在CKE0和CKE1与子对应;从信号的角度来看,也就不存在所谓的CKE和CS#了。

- 在DDR3及更高版本协议的情况下,DDR SDRAM数据传输速率更快,其信号的质量更容易受影响,为了减少DDR信号质量对速度的影响,DDR相关协议对DDR的数据端管脚设计了终端匹配电阻,而终端匹配电阻的使能除了要先打开DDR的内部开关外,还需要外部的ODT信号进行精准控制。在写数据通道中,ODT信号会被用到。

- CKE、CS#、ODT、ZQ信号属于同一种类型,即同一片Rank存在一组CKE、CS#、ODT、ZQ信号。

| 分类 | 信号名 | 方向 | 源 | 描述 |

|---|---|---|---|---|

| 信号组 | RAS#/A16、CAS#/A15、WE#/A14 | IN | 命令输入 | 此组命令与CS_n可构成当前命令的输入编码,有多重含义。例如:当ACT命令时,即ACT#为低电平时,这三个信号作为地址线使用;当ACT#为高电平时,这三个信号作为命令编码使用。例如:读、写等其他命令操作都可通过这三个命令组合实现 |

-

RAS#、CAS#、WE#这三个信号与片选CS#信号,共同组成了DDR的命令信号组,同时CKE也参与了信号组,只是CKE大多数时间为高。(RAS: Row Address Strobe,行地址选通脉冲;CAS: Column Address Strobe,列地址选通脉冲;)

-

DDR bank的选中过程即为DDR的激活,即ACTIVE也可认为是DDR的打开过程。而DDR bank的关闭则称子为DDR的预充电,即Precharge。

| 分类 | 信号名 | 方向 | 源 | 描述 |

|---|---|---|---|---|

| 地址和数据信号 | BA0-BA2 | IN | Bank地址信号 | Bank Address,Bank选择 |

| A0 - A15 | IN | Column/Row行列地址信号 | Address地址总线:在ACT命令中作为行地址,在读写命令中作为列地址,从而可定位存储阵列中精确位置。A10/AP、A12/BC#可以作为额外的地址总线使用。在MRS命令中,地址总线还作为操作码使用,即写入模式寄存器的值。 | |

| A10/AP | IN | 自动刷新 | Auto-Precharge,此位可控制读写操作完成后是否进行自动刷新操作,高电平为开启自动刷新操作,低电平为关闭自动刷新操作。该命令与读写命令同时使用。在PRE命令中,A10还可作为是否进行全bank操作的开关。如果仅有一个bank进行刷新,则由bank地址来确定哪个bank来进行操作。 | |

| A12/BC# | IN | 突发突变 | Burst Chop,主要用来控制burst突发长度。通常情况下,DDR3的burst length的最小单位是8bit,而在一些特殊条件下(on-the-fly模式)Burst也可进行4bit传输,而砍掉剩下的4bit。在on-the-fly模式下,BC#信号会在读写数据期间进行采样,动态切换burst的传输长度为4bit或是8bit。 | |

| DQ | IN/OUT | 数据信号 | Data input and output,双向数据总线:(低8位数据和高8位数据信号线,共16位数据信号线)若模式寄存器中使能了CRC功能,那么在数据burst结束时就会附加一段CRC码。若MR4中的A4为高电平,那么在测试中DQ0-3中的任意一根DQ信号都可以代表VREF的电平。 | |

| DQU, DQL DQS, DQS# DQSU,DQSU# DQSL,DQSL# |

IN/OUT | 数据选通信号 | Data Strobe,输入时与写数据同时有效,输出时与读数据同时有效。与读数据是边沿对齐的,但是跳边沿位于写数据中心。在x16系统中,DQSL对应DQL0-7,DQSU对应DQU0-7;DQS、DQSL、DQSU分别与DQS#、DQSL#、DQSU#对应为差分信号对。DDR3 SDRAM仅支持选通信号为差分信号,不支持单根信号的选通信号。 | |

| TDQS, TDQS# | OUT | 终端数据选通 | Terminal Data Strobe,TDQS与TDQS#仅在x8系统中运用。当MR1寄存器中的A11为高电平时,DRAM就会使能相似终端阻抗(same terminal resistance)功能,同时TDQS与TDQS#将会应用于DQS与DQS#。当MR1寄存器中的A11为低电平时,DM/DBI/TDQS将会作为数据掩码或者数据总线翻转功能使用,且A12、A11、A10与TDQS#都不会使用。在x4和x16系统中DRAM的TDQS必须是禁用的,也就是MR1的A11永远为低电平。 | |

| DM, (DMU), (DML) | IN | 数据掩码、数据总线倒置 | Data masked,DM作为写数据的掩码信号,当DM为高电平有效时,与DM同一拍的写数据是无效的。DM在DQS的两个条边沿都采样。在x16设备中,DMU对应数据高8位,DML对应数据低8位。TDQS仅支持x8设备。 |

- 除了A10和A12之外,RAS#/A16、CAS#/A15、WE#/A14也可以作为额外的地址总线使用,其中A16还有RAS#功能,A15有CAS#功能,A14有WE#功能,A12有BC#功能,A10有AP功能。

- DQS,DQS#信号与DQ是数据信号是源同步的,两者属于伴生信号,其中DQS信号类似于Clk用来控制DQ的有效性。通常情况下,一个DQS控制一个8bit的数据,一个DQM(DM)控制一个8bit的数据。

1个DQS,1个DQM,8个DQ组成一组Bytelam,对于一个16bit的DDR颗粒,则有两组Bytelame。- TDQS,TDQS#信号不常用。

| 分类 | 信号名 | 方向 | 源 | 描述 |

|---|---|---|---|---|

| DDR4新增信号 | BG0 - BG1 | IN | Bank选择 | BG0-BG1可以选择当前的ACT、RD、WRT或者PRE命令是对哪一个Bank Group进行操作。在MRS命令中,BG0也参与模式寄存器的选择。在×4、×8系统中,有BG0与BG1。在x16系统中,仅有BG0。 |

| ALERT_n | IN/OUT | 报警信号 | 警示:该信号可代表DRAM中产生的多种错误,如若命令与地址的奇偶校验错误、CRC校验错误。当出现CRC校验错误时,在对应周期中该信号将拉低,然后在重新恢复成高电平。在奇偶校验错误时,在对应周期中该信号拉低,在内部,当DRAM的操作周期完成时,该信号就会恢复成高电平。在连通性测试中,此信号在输入状态下工作,但是是否使用此信号,取决于系统的整体规划,若该信号没有使用,则需要在板上将该信号连接至VDD | |

| TEN | IN | 测试模式使能信号 | 连通性测试使能:(高电平使能测试模式。正常操作过程中,必须拉低) | |

| PAR | IN | 命令/地址信号的奇偶校验使能 | 可通过寄存器禁用或者使能。DDR4 SDRAM是支持奇偶校验的。一旦MR5被使能,DRAM将计算ACT#、RAS#/A16、CAS#/A15、WE#/A14、BG0-BG1、BA0-BA1、A0-A17的奇偶性。以上所有的输入的奇偶性都应该在时钟的上升沿与CS#为低电平时保持住。 | |

| ACT# | IN | 命令激活信号 | 这个信号为低电平时,可以通过A[14:16]地址信号线选择激活命令的行地址。为高电平时,Address信号线正常使用。此信号有效时,RAS#/CAS#/WE#将作为行地址的A16/A15/A14来使用 |

- DDR4新增加了一些信号,其中常用到的有Bank group地址选择信号。一个DDR4 SDRAM 的DDR颗粒中中通常会包含多个Bank group,而每个Bank Group又会包含了多个Bank,因此在地址选择时应该首先选择BG地址。

| 分类 | 信号名 | 方向 | 描述 |

|---|---|---|---|

| 电源信号 | VDD | supply | 电源电压(core电源),1.5V+/-0.075V |

| VSS | supply | 地 | |

| VDDQ | supply | DQ电源电压(IO电源),1.5V+/-0.075V | |

| VSSQ | supply | DQ地 | |

| VREFCA | supply | 地址、控制、命令(CA)的参考电压,VREFCA在所有时刻(包括自刷新)都必须保持规定的电压 | |

| VREFDQ | supply | 数据(DQ)的参考电压,VREFDQ在所有时刻(除了自刷新)都必须保持规定的电压 | |

| ZQ, (ZQ0), (ZQ1), (ZQ2), (ZQ3) | supply | 输出驱动校准的外部参考电压,这个引脚应该接240Ω电阻到VSSQ |

二、DDR颗粒的地址映射关系

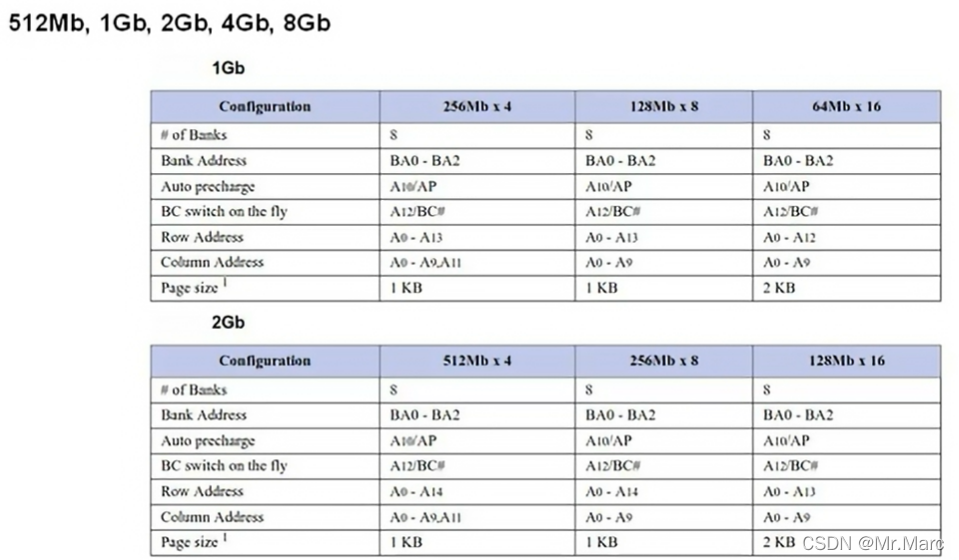

DDR协议规定了DDR Memory颗粒容量的类型多样,包含512M,1Gb,2Gb,4Gb,8Gb等不同种类,每一种Memory颗粒的又分为x4,x8,x16三种不同型号存储单元,各容量颗粒类型及其型号如下表:

以1Gb容量的DDR 颗粒为例对表格进行说明:

- 表中x4,x8,x16三种不同型号表明颗粒的存储单元数据位宽分别为4bit,8bit,16bit不同类型,各类型的地址及其空间分配是不同的(也有相同之处,如bank数量都为8),详情见表格的列。

- 以x16类型的颗粒为例,可见其行地址(Row Address)为A0-A12,共13bit,即有8K(2^13)个行地址,其列地址(Column Address)为A0-A9,共10bit,即有1K(2^10)个列地址。

- Page size,即每行的存储的容量。Page size = 列地址数量 x 存储单元数据位宽 = 1K x 16bit = 2KB。

- 颗粒的总容量 = Banks x Row Address x Column Address x 存储单元数据位宽 = 8 x 8K x 1K x 16bit = 64M x 16bit = 1Gb。

- A10不会被列地址使用,这是由于只有在发起读写命令时才会使用到列地址,而此时A10会与列地址进行搭配使用表明表明DDR的Auto-precharge状态,故不作为地址使用。

- A10和A12会被行地址使用,这是由于在发起读写命令之前就会用到行地址,此时行地址处于ACTIVE激活状态,不需要用到Auto-precharge和BC Switch功能,故A10和A12会被作为地址使用。

智能推荐

前端工程与性能优化-程序员宅基地

文章浏览阅读881次。前端工程与性能优化 · Issue #3 · fouber/blog https://github.com/fouber/blog/issues/3

yolov5测试单张图片-程序员宅基地

文章浏览阅读4.1k次,点赞2次,收藏20次。yolov5测试单张图片,返回一个列表[类别,置信度,x,y,w,h]from numpy import randomimport torchfrom models.experimental import attempt_loadfrom utils.datasets import LoadStreams, LoadImagesfrom utils.general import ( check_img_size, non_max_suppression, apply_classifier_yolov5测试单张图片

SQL做的能改成Oracle吗,从SQL改写到SQL重写,什么样的SQL才是好SQL?(黄浩)-程序员宅基地

文章浏览阅读88次。从SQL改写到SQL重写,什么样的SQL才是好SQL?黄浩 2016-12-14 10:02:26作者介绍黄浩,现任职于中国惠普,从业十年,始终专注于SQL。十年一剑,十年磨砺。3年通信行业,写就近3万条SQL;5年制造行业,遨游在ETL的浪潮;2年性能优化,厚积薄发自成一家。在生活中,很多时候我们会有这样的体悟:问题要么不出,一旦出现,会像多诺米骨牌一样,会连锁引发诸多相关问题,让我们疲于应付。..._黄浩 sql

.NET 学习教程下载地址_.net课程下载-程序员宅基地

文章浏览阅读578次,点赞2次,收藏2次。==============================================================================================================教程&电子书==============================================================================================================C#入门经典_.net课程下载

STM32F7 + FREERTOS + LWIP 接收数据从网卡到应用层完整流程_stm32f7 lwip-程序员宅基地

文章浏览阅读3.8k次,点赞2次,收藏8次。来来来,这里解释下从网卡PHY到IP层的数据接收流程:这里是以函数调用方式来体现:netif_add——》ethernetif_init——》low_level_init——》ethernetif_input——》low_level_input和tcpip_input——》ethernet_input——》ip4_input(etharp_input、pppoe_disc_input)——》udp..._stm32f7 lwip

Linux服务器Input/output error错误_linux 写入文件到挂载的nas下提示failed to close...input/output-程序员宅基地

文章浏览阅读1.6w次。报错系统Centos报错提示Input/output error检查服务器机器中多硬盘是否其中有一块硬盘坏掉了。第二种可能:RAID阵列可能有问题。。。_linux 写入文件到挂载的nas下提示failed to close...input/output error

随便推点

UNITY中判断两个点之间距离的方法_unity 判断两个距离-程序员宅基地

文章浏览阅读3.1k次,点赞3次,收藏4次。Vector3.SqrMagnitude与Vector3.Distance_unity 判断两个距离

Idea设置未使用的方法,变量的提示颜色_idea 更改未使用变量的颜色-程序员宅基地

文章浏览阅读2.8w次,点赞6次,收藏14次。修改未被调用的变量,方法的提示,方便观赏代码_idea 更改未使用变量的颜色

在Linux系统下C语言编译过程的四个步骤_linux下编写一个c程序的基本过程分为几部分?-程序员宅基地

文章浏览阅读2.7k次,点赞7次,收藏23次。1. 简介C语言程序从源代码到可执行文件(二进制文件)都经历了那些过程?本文以Linux下C语言的编译过程为例,讲解C语言程序的编译过程。以hello.c文件为例:#include <stdio.h>int main(){ printf("hello world!\n");}在linux下编译C程序:$ gcc hello.c -o hello # 编译$ ./hello # 执行hello world! # 输出文本2. 编译的步骤gcc命令编译C语言的过程中_linux下编写一个c程序的基本过程分为几部分?

pyqt5界面开发-制作程序集合桌面-基本的框架_用pyqt做程序集合的界面-程序员宅基地

文章浏览阅读340次。pyqt5界面开发-制作多个小程序-基本的框架和思路最近现在无事,看到了电脑桌面,又想到了最近入门的pyqt5,再看看以往的程序,想到了可不可以做一个集成的UI桌面_用pyqt做程序集合的界面

对网站商城源码的研究分析 分享大量源码下载_chengren 电影-程序员宅基地

文章浏览阅读2k次。第一部分(1-6):前端纯静态网页模板无后台+大量网站设计素材 1:PC模板: 9900套响应式html5+css3网页模板【页面齐,二级,三级页均有,含中文模板】 2:PSD模板:3000套PSD模板+600套Flash酷站源文件+千套矢量ICO图标 3:手机模板:2000套各行业中文手机..._chengren 电影

ORA-39143: 转储文件 "F:\ora10G_expdp\ic_price_fromlufang.dmp" 可能是原始的导出转 储文件...-程序员宅基地

文章浏览阅读441次。连接到: Oracle Database 10g Enterprise Edition Release 10.2.0.1.0 - ProductionWith the Partitioning, OLAP and Data Mining optionsORA-39001: 参数值无效ORA-39000: 转储文件说明错误ORA-39143: 转储文件 "F:\ora10G_expdp\ic_pri..._ora39143