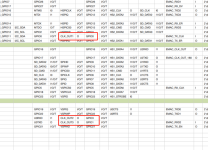

”mclk“ 的搜索结果

介绍audio调试过程中遇到的mclk异常,mclk没有输出,sdi没有信号的问题

基于多时钟的处理,在跨时钟域的处理上有优势

camera

LRCLK BCLK MCLK

时钟频率需要用示波器查看,MCLK为1.05MHz, SMCLK 为1.05MHz,ACLK为32.768kHz。学习MSP430F5529 Drivelib库函数 GPIO模块使用。3. GPIO 引脚复用,输出MCLK SMCLK ACLK时钟频率。2. 按键控制LED亮灭, 软件延时消...

硬件上,RK 芯片端 i2s mclk 引脚连接外部 codec 芯片 mclk 引脚,为外部芯片提供 mclk 时钟。软件上,需要对 mclk 做使能处理。 DTS配置 不同平台对应的时钟名称不一样,下述只举例 RK3399 和 RK3288 平台配置,...

前言MCLK是平台baseband提供给camsensor的正常工作的频率,Qcom平台一般未24MHz,由其他时钟源分频而来,实测在23.8MHz左右。在打开相机的时候,才可以测到这个时钟。camsnesor可以使用平台提供的时钟或者自带时钟源...

人声一般是16kHz,8kHz等采样,因为人声的频率比较低,男:低音82~392Hz,基准音区64~523Hz,男中音123~493Hz,如下图,位深是16bit,两个字节。:就是模拟信号转为数字信号时的采样频率,根据奈奎斯特采样定理...

转:https://blog.csdn.net/lugandong/article/details/72468831一、拿512fs说话:看图知道采样的位深是32bit(位),左右声道各占了8*32BCLK,那一个完整的LRCLK一共8*32*2=512BCLK。其实xxxfs就是这么算出来的,也是...

MCLK是平台baseband提供给camsensor的正常工作的频率, Qcom平台一般未24MHz,由其他时钟源分频而来,实测在23.8MHz左右。 在打开相机的时候,才可以测到这个时钟。 camsnesor可以使用平台提供的时钟或者自带时...

主要mclk使用的引脚为IMX8MP_CLK_IPP_DO_CLKO2,可以通过此引脚定义的不同时钟来分频设置clk。 如16M可以通过400M整分。 在相应dts中修改以下三行: 为16M clk assigned-clock-parents = <&clk IMX8...

有哪个兄弟知晓I2S中主设备输出的时钟MCLK为什么是FS(采样率)的256倍或者384倍吗

Platform: RK3399 OS: Android 7.1 Kernel: v4.4.83 Power Domain: audio codec的clk被关联到power domains中管理。 rk3399.dtsi: i2s0: i2s@ff880000 { //...... clock-names = &...a

MSP430基础时钟模块包含以下3个时钟输入源。 一、4个时钟振荡源 1、LFXT1CLK:外部晶振或时钟1低频时钟源低频模式:32768Hz高频模式:(400KHz-16MHz) 2、XT2CLK:外部晶振或时钟2高频时钟源(400KHz-16MHz)3、...

一、拿512fs说话:看图知道采样的位深是32bit(位),左右声道各占了8*32BCLK,那一个完整的LRCLK一共8*32*2=512BCLK。其实xxxfs就是这么算出来的,也是固定的,当你定了几个channel,多少位深,就几乎可以确认是多少...

RK3288 7.1 Camera IMX307 mclk 37.125M补丁 1. 在调试imx307 效果的时候,预览图像的时候始终有些轻微抖动,后面发现是camera是时钟不对。 imx307要求是时钟是37.125M,设置的时钟也是37.125M,而平台分出来是...

RK356X CAM MCLK配置说明

转:https://blog.csdn.net/lugandong/article/details/72468831一、拿512fs说话:看图知道采样的位深是32bit(位),左右声道各占了8*32BCLK,那一个完整的LRCLK一共8*32*2=512BCLK。其实xxxfs就是这么算出来的,也是...

MSP-EXP430G2 LaunchPad MCLK SMCLK ACLK默认时钟频率, 有图,有代码示例

刚开始用 TI MSP430F5529,在看了两位大佬的文章...系统默认时钟,主时钟MCLK是1.5MHz左右,子时钟SCLK是1.5MHz左右,辅助时钟ACLK是32.768kHz。新建工程,复制代码到main.c,编译下载程序,用示波器查看输出信号频率。

针对部分需要开机后就一直提供 I2S MCLK 才能正常工作的codec,软件端加下述patch即可。 代码路径:kernel/sound/soc/rockchip/rockchip_i2s.c diff --git a/sound/soc/rockchip/rockchip_i2s.c b/sound/soc/...

平台内核版本安卓版本RK3399Linux4.4Android7.1问题描述:机器用于视频会议,回声消除用了XMOS的硬件IC,IC供应商说IIS的LRCLK要为48K,而且MCLK也必须要为24.576M,而且要一直给出来。XMOS芯片只需烧录供应商对应的...

PCLK:pixel clock, used for MCU camera sensor controller to capture ...MCLK:master clock for sensor logical chip. HSYNC and VSYNC used for MCU camera sensor controller to capture the pixels l...

也称IIS系统时 钟,一般是采样频率的256倍、512倍,384倍。假设采样率是48K,MCLK输出的时钟是采样的256倍,则MCLK会输出 48K*256 = 12.288MHz。

也称IIS系统时钟,一般是采样频率的256倍、512倍,384倍。假设采样率是48K,MCLK输出的时钟是采样的256倍,则MCLK会输出 48K*256 = 12.288MHz。

int alink_init(ALINK_PARM *parm)文件中会 使能 MCLK 时钟,把对应的代码注释掉即可。

推荐文章

- NSFuzz:TowardsEfficient and State-Aware Network Service Fuzzing-程序员宅基地

- 刘睿民畅谈大数据:政府应紧急设立首席数据官-程序员宅基地

- nginx 编译安装依赖包_nginx编译怎么添加新的依赖库-程序员宅基地

- Python+OpenCV+Tesseract实现OCR字符识别_python + opencv + tesseract-程序员宅基地

- 微型计算机主板上的主要部件,微型计算机主板上安装的主要部件-程序员宅基地

- 推荐一款可匹敌国际大厂的国产企业级低无代码平台_国产私有化 无代码-程序员宅基地

- UE4 蓝图 实现 数组的边遍历边删除_ue4 数组删不掉-程序员宅基地

- python爬虫之bs4解析和xpath解析_from bs4 import beautifulsoup xpath-程序员宅基地

- MySQL配置环境变量-程序员宅基地

- VGG16进行微调,训练mnist数据集_vgg16 tensorflow 2 mnist-程序员宅基地