flow官网“reference”的自用翻译 包含qflow流程,使用,语法_yosys blif-程序员宅基地

此文为:flow官网“reference”的自用翻译,不是官方完整版本。仅作为自己学习过程中的记录,顺便发出来与各位分享。

大部分为机翻,有错误欢迎批评指正。

官网:Qflow (opencircuitdesign.com)

一些常用英文:

综合:synthesis;布局:placement;布线:route;版图:layout;网表:netlist

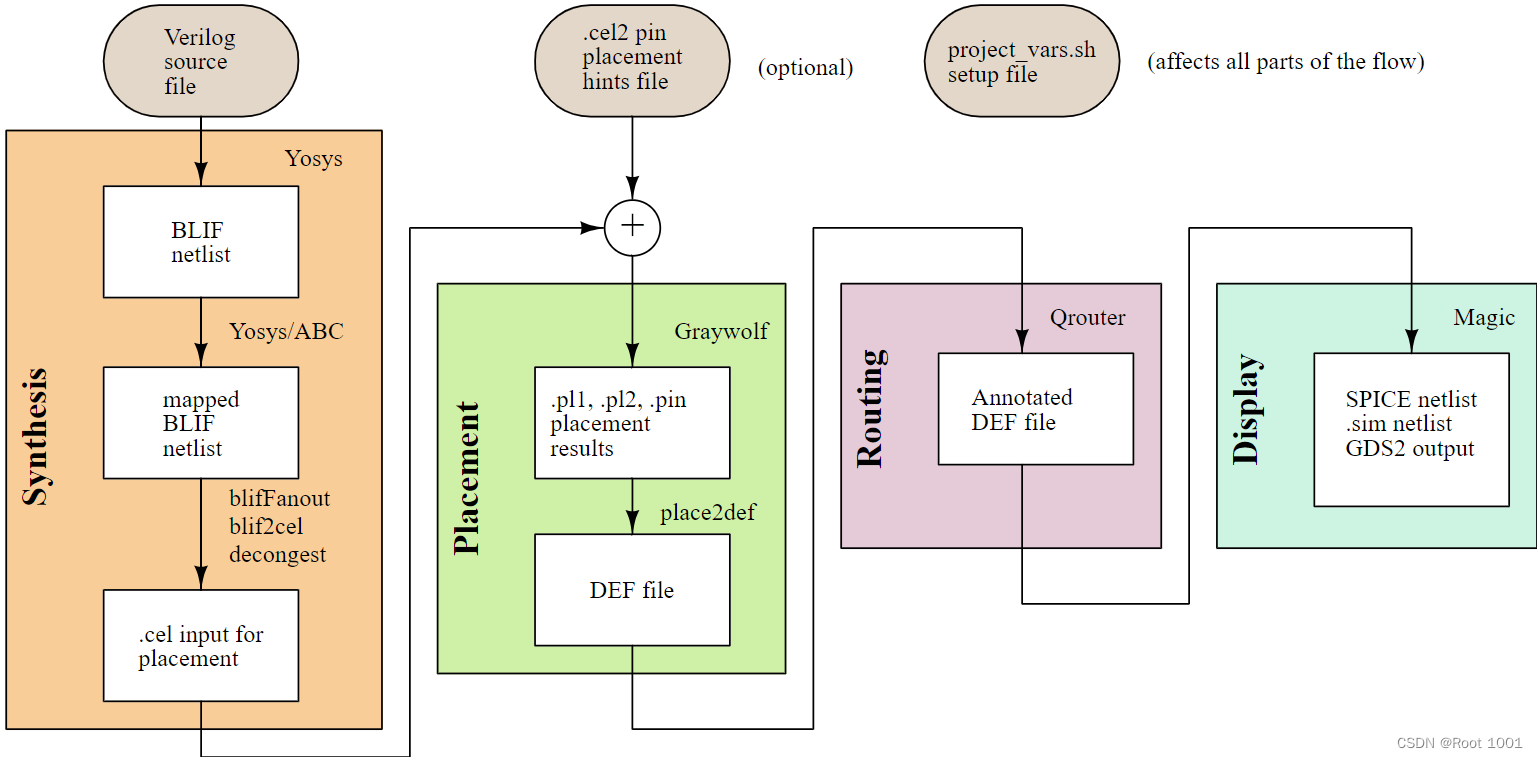

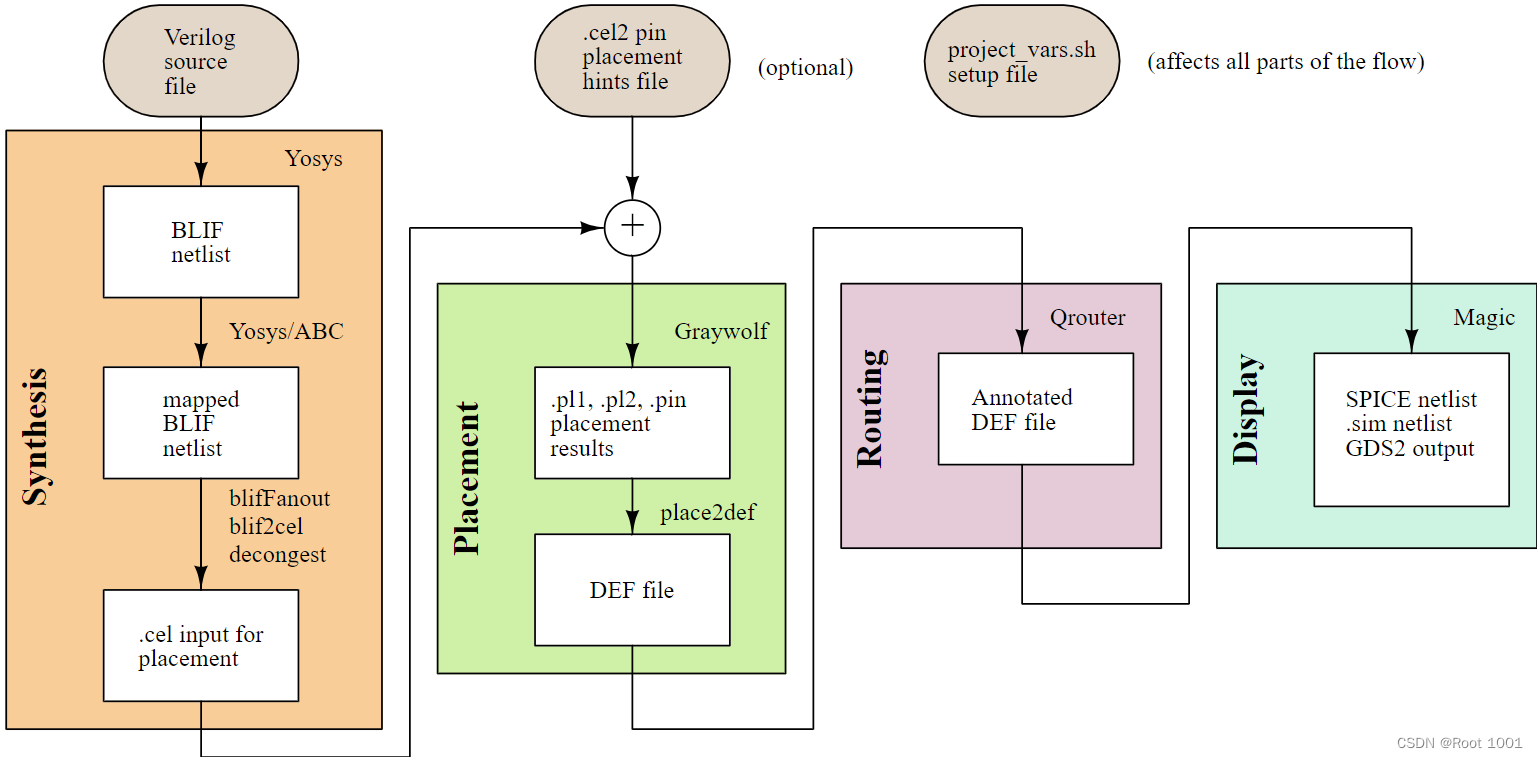

流程

综合Synthesis

- yosys frontend

Yosys 读取 Verilog 源文件,综合,优化, 并以 BLIF 格式写入网表。ypostproc 根据流中更下游的工具的需要,清理yosys输出中的一些语法。

- blifFanout分析每个栅极输出负载的网表, 并尝试通过使用具有更高驱动强度的逻辑单元来保持每个输出的延迟小于75ps的默认值。 The "-l latency" option specifies the maximum output latency, in ps. Nets with high fanout can be reduced by buffering using the "-c cap" option to specify a maximum load capacitance on an output, in fF, but fanout reduction is better handled by the resynthesis stage (see below), which takes placement into account when breaking a network into groups.

- blif2cel 脚本获取最终网表 文件,并将其转换为graywolf布线工具。In addition, it takes a template parameter file for graywolf "techname.par", and places it in the layout subdirectory for use by graywolf, and renames it "source_name.par

布局Placement

执行Graywolf,并为设计中的所有数字标准单元实例生成一个位置。放置阶段的运行时间大约与设计中的标准单元实例的数量成正比。放置阶段的输出是三个文件,格式仅供graywolf和转换其输出的qflow脚本使用。

扇出减少Fanout Reduction

blifFanout工具将高扇出节点分解为缓冲树,以减少节点上的总延迟。该方法将目标节点任意连接到缓冲区,并依赖于graywolf放置工具使用的方法来自动调整这些连接以实现最佳布线。这是在初始综合步骤中完成的单步方法。调整后的连接在放置后被回注到网表中。

布线Routing

qrouter生成详细的布线,并且输出一个带注释的DEF文件,包含详细信息。source_name.def,即最终的物理电路。

显示Display

工具magic (version 8.0)读取LEF文件,然后读取最终的DEF文件,并在布局查看器layout viewer中显示结果。

使用(项目文件夹和文件介绍)

项目文件夹包括:

source:放Verilog源代码

synthesis:寄存器级别RTLVerilog输出,工作文件

layout:DEF输出,工作文件

qflow运行

执行:qflow source_name

(eg:如果你的Verilog源文件是circuit.v,那就qflow circuit)

执行后会生成这三个文件:

qflow_vars.sh

包含所有工具所需的项目相关变量,确定项目路径、qflow可执行路径和所使用的技术。

qflow_exec.sh

包括完成qflow流程所需的命令。

当没有给qflow选项时,文件qflow_exec.sh将有被注释的命令。这允许用户一次取消一个工具链命令的注释,并独立运行每个工具。在大多数情况下,设计周期需要检查每个步骤的结果并根据需要进行调整。最终,流程将是稳定的,并且所有步骤都可以运行。

以下是该文件包含的典型的一系列命令:

synthesize.sh options

Logic synthesis, standard-cell mapping, and load balancing, fanout reduction, and decongestion.(逻辑综合,标准单元映射,负载平衡,扇出减少和去拥塞。)

vesta.sh options

Static timing analysis (without back-annotated parasitics).(静态时序分析(没有反向注释寄生))

placement.sh

Placement of standard cells with buffer tree optimization(标准单元放置与缓冲树优化)

router.sh

Detail routing(详细布线)

vesta.sh -d options

Static timing analysis (with back-annotated parasitics).(静态时序分析(带有反向注释寄生))

migrate.sh

cleanup.sh

Removal of temporary working files(删除临时工作文件)

display.sh

Display of the final layout(显示最终版图)

这些额外的功能在qflow 1.2中可用:migrate.sh options

Generation of layout and abstract views, and netlist extraction.(生成版图和抽象视图,以及网表提取。)

drc.sh options

DRC (Layout design rule check) analysis(DRC(版图设计规则检查)分析)

lvs.sh options

LVS (Layout vs. schematic) analysis(LVS(版图vs电路图)分析)

gdsii.sh options

Generation of GDS mask data(生成GDS掩码数据)

Qflow 1.0版本有一个额外的再综合,和第二个放置阶段,在Qflow 1.1版本被合并为一个步骤:

resynthesize.sh

Placement-based fanout reduction, and load balancing(基于布局的减少扇出和负载均衡)

placement.sh

Placement using modified netlist from resynthesis(使用再综合的修改后的网表的布局)

project_vars.sh

这是一个空文件,但是可以对其进行编辑来控制命令行(来控制工具)。该文件永远不会被覆盖,因此可以保留用户选项。

Qflow语法和选项 qflow [options] [actions] source_name

Qflow命令行格式:

qflow [ options] [ actions] source_name

选项和操作如下:

选项【options】

-T technology

--tech technology

如果未指定technology,则搜索目录中现有的文件qflow_vars.sh,如果存在,则对其进行解析,以查看先前为项目指定的技术,并选择该技术作为技术。否则,使用默认技术(osu035)。如果技术是通过名称指定的,那么它应该是一个被命名的目录,可以在qflow安装位置的子目录“tech”下找到它。(一般在 "/usr/local/share/qflow/tech/"), 或者在当前工作目录中,或者在环境变量QFLOW_TECH_DIR指示的目录中。在technology目录中必须有一个名为technology.sh的文件,其中包含qflow使用的所有配置设置(请参阅下面关于添加新技术的部分)。

-p project

--project project

如果qflow没有在顶级项目文件目录下运行,则会提供此选项。project的值是qflow应该转存文件的项目目录,并且这些文件中的所有指针都指向指定的项目目录“project”。

-t toolname

--tool toolname

此选项指定合成流要使用的非默认工具。

-h

--help

-v

--version

操作 [actions]

所有操作都在输出文件qflow_exec.sh中表示。 但是,如果在命令行上调用了特定的操作,那么与这些操作相关的那些命令将在文件中去除注释。当qflow生成命令文件时,这些操作将按顺序执行。

有两个操作很容易记住,并且包含了最重要的步骤,因此您不必记住要添加到命令行中的所有步骤的所有名称:

1. build

Run these steps in sequence: synthesize, place, buffer, route (see below)(按顺序运行这些步骤:综合、布局、缓冲、布线(见下文))

2. all

Run these steps in sequence: synthesize, place, buffer, route, clean, display (see below)(按顺序运行这些步骤:综合、布局、缓冲、布线、清理、显示(见下文))

单个合成步骤如下:

synthesize

Run the verilog synthesis (yosys, or, in qflow-1.0 only, Odin-II and ABC) and load balancing (blifFanout) and node fanout reduction (blifFanout, in qflow-1.1 only)

sta

Run static timing analysis (vesta)

place

Run the placement (graywolf)

buffer

(qflow 1.0 only)

Perform fanout reduction, and rerun the load balancing and placement (clocktree, blifFanout, and graywolf). Note that qflow 1.1 does this in one pass during the "synthesize" stage.

route

Run the detail router (qrouter)

backanno

Run static timing analysis (vesta) with back-annotated delays

migrate

Create layout and abstract views, and extract netlist from layout (qflow 1.2 and higher).

drc

Run design rule checks on the layout (qflow 1.2 and higher).

lvs

Run layout vs. schematic check (qflow 1.2 and higher).

gdsii

Generate GDS mask layer output (qflow 1.2 and higher).

clean

Clean up temporary files in all subdirectories.

display

Display the layout result (magic)

环境变量

以下环境变量对qflow有用:

QFLOW_TECH_DIR

使用变量定义作为可以找到技术目录的位置。这个环境变量覆盖qflow安装路径中的默认位置。可以在命令行上使用“-T”选项覆盖它。

QFLOW_TECH

使用变量定义作为目录的名称,在该目录中可以找到用于合成的目标技术的技术信息。这个环境变量覆盖了qflow发行版提供的默认技术,即“osu035”。可以在命令行上使用“-T”选项覆盖它。

QFLOW_PROJECT_ROOT

使用变量定义作为顶级项目目录的名称。此环境变量覆盖默认的项目位置,即当前工作目录(“.”)。可以在命令行上使用“-p”选项覆盖它。

未定义的操作

对于大多数项目,用户希望控制综合过程的许多方面。文件“project_vars.sh”是此类用户选项的主要位置。大多数选项都是通过在文件中设置shell变量来声明的。qflow可以识别以下shell变量。这个列表经常更新。比这里列出的选项更多;这里只描述用户感兴趣或有帮助的选项设置:

第一组选项(来自qflow版本1.4)选择每个步骤使用哪个工具。“工具”是从qflow_exec.sh文件调用的shell脚本。该脚本必须命名为tool_name.sh,安装在qflow脚本安装目录下(默认为/usr/local/share/qflow/scripts/)。在大多数情况下,工具名称只是提供流程步骤的应用程序的名称,但是在一个工具有多种用途的情况下(如magic),脚本名称需要是唯一的(例如,magic_drc和magic_gds)。

要向qflow添加新工具,需要编写一个shell脚本包装器,该包装器使用适当的选项和参数调用新工具。新的工具在可用时被添加并集成到qflow中。

synthesis_tool=tool_name

Currently supported tools: yosys

placement_tool=tool_name

Currently supported tools: graywolf and replace

sta_tool=tool_name

Currently supported tools: vesta, opensta, and opentimer

router_tool=tool_name

Currently supported tools: qrouter

migrate_tool=tool_name

Currently supported tools: magic_db

lvs_tool=tool_name

Currently supported tools: netgen_lvs

drc_tool=tool_name

Currently supported tools: magic_drc

gds_tool=tool_name

Currently supported tools: magic_gds

display_tool=tool_name

Currently supported tools: magic_view

第二组选项适用于流程的每个步骤:

source_file_list=filename

Qflow让yosys自动检测设计中的所有模块,并创建要包含的文件列表以读取所有模块,以防verilog源没有显式包含每个文件。但是,如果文件不在源目录中,则不会找到它们。如果由于这个原因或任何其他原因,合成脚本无法找到所有需要的源文件,则可以将文件列表放入一个文件中,每行一个源文件,并将该文件作为source_file_list的值filename传递。

is_system_verilog

Qflow将自动检测扩展名为“.sv”的系统verilog文件。如果文件没有被正确检测为系统verilog,则启用此选项。

hard_macros="macro1 macro2 ..."

Qflow通常使用标准单元进行设计。但是,设计可能包含不属于标准单元格集的其他宏的实例。为了使合成流能够使用硬宏,所有这些宏都需要以空格分隔的名称列表列出,并用引号括起来。

yosys_options="text"

传递给yosys进行合成的选项。

(e.g., "iopadmap -inpad ..." 为输入信号添加缓冲区), 然后设置yosys_options为 "-s newscript.ys".

yosys_script=filename

filename 表示文件的名称 包含要传递给 Yosys 以执行 合成的主要部分。文件的内容 入到正常的合成脚本中 用于加载必要 Verilog 源文件的命令 以及将综合结果映射到 标准单元格集。因此,它不同于通过 yosys_options中的“-s filename”(见上文),它完全取代了 整个合成脚本。filename 的内容是以下标准的直接替代 qflow 使用的合成命令:

proc; memory; opt; fsm; opt

yosys_debug

如果定义了这个变量,那么在优化期间不会将“-purge”选项传递给yosys,以便保留所有内部节点名称。这导致了一个更大的布局,插入了许多非功能缓冲区来维护具有特定信号名称的网络(对于来自分层verilog源的布局尤其普遍)。结果允许在模拟和调试期间探测所有信号名,但通常不是实现中想要的结果。

nobuffers

如果定义了此变量,则模块输出 将无缓冲;也就是说,模块输出引脚将 直接连接到寄存器输出,可以 也可以内部连接到其他输入。这 默认行为是缓冲寄存器输出,因此 输出引脚负载不能改变内部 电路的定时特性。缓冲是 强烈推荐。不这样做的典型原因 缓冲是合成一个小的子电路,如 作为驱动模拟电路的解码器,其中所有 输出负载小,电路面积 限制。

inbuffers

指定应缓冲所有模块输入。 缓冲输入有助于保持输入时序 准确,因为信号上升缓慢和/或 秋季时间可能会有明显不同 在整个数字布局中输入门的时间。 缓冲确保到达的信号是 用锋利的边缘重复,合成是 能够更好地控制时间。

postproc_options="text"

这些选项被传递给vlog2Verilog工具,用于在合成后操作网络列表。最常见的用法是将value设置为“-anchors”,这告诉qflow将天线捆绑添加到所有模块输入(假设标准单元集具有天线捆绑单元)。

xspice_options="text"

该选项提供要传递给spi2xspice.py脚本的值。在当前版本(qflow-1.4)中,spi2xspice.py没有在标准单元中提供精确的计时,因此对每个单元使用平均延迟值。每个值(选项如下所示)作为spice类型的值给出,即使用数字和度量前缀(例如,“10n”表示10纳秒):

-io_time=value

信号进出数字块的上升和下降时间

-time=value

门输出的上升和下降时间

-idelay=value

在门输入处的输入延迟

-odelay=value

门的吞吐量延迟

-cload=value

门输出负载电容

vesta_options="text"

静态时序分析仪Vesta的一个更重要的选项是“——period值”,用于指定电路操作的预期最小时钟周期。时钟周期以皮秒(ps)为单位。选项“-l load”指定电路的典型输出引脚负载电容,当集成到更大的环境中并在此环境中工作时。

opentimer_options="text"

传递给OpenTimer的选项列表(参见OpenTimer文档)。

opensta_options="text"

传递给OpenSTA的选项列表(参见OpenSTA文档)。

nofanout

如果设置了nofanout,则不运行vlogFanout工具。这可以防止门调整大小和缓冲的大扇出网,并产生时钟树。建议仅在输入源是一个已经包含大小门的网表,或者合成工具(或放置工具)执行时钟树插入和/或门调整大小的情况下使用此选项。

fanout_options="text"

blifFanout只有几个qflow没有使用的选项:“-l”指定一个时间值,以ps为单位,即通过电路中任何门的目标最大时间。“-c”指定电路任意输出引脚上期望的最大容性负载,单位为fF。默认值是75ps延迟和25fF电容。

initial_density=value

该选项设置要使用的初始密度,其中密度值定义为包含主动路由(即不填充或decap)单元格的布局区域的百分比。对于小单元格(< 1000个栅格),不应该指定密度(默认为1,或者没有填充单元格,除非需要拉直布局区域的边缘)。对于大型单元,特别是具有密集组合逻辑区域(如乘数)的单元,指定初始密度对于使设计路由至关重要。

graywolf_options="text"

传递给graywolf的选项列表(请参阅graywolf文档)。

qrouter_options="text"

(后面的我基本用不到,没写入进来。)

智能推荐

攻防世界_难度8_happy_puzzle_攻防世界困难模式攻略图文-程序员宅基地

文章浏览阅读645次。这个肯定是末尾的IDAT了,因为IDAT必须要满了才会开始一下个IDAT,这个明显就是末尾的IDAT了。,对应下面的create_head()代码。,对应下面的create_tail()代码。不要考虑爆破,我已经试了一下,太多情况了。题目来源:UNCTF。_攻防世界困难模式攻略图文

达梦数据库的导出(备份)、导入_达梦数据库导入导出-程序员宅基地

文章浏览阅读2.9k次,点赞3次,收藏10次。偶尔会用到,记录、分享。1. 数据库导出1.1 切换到dmdba用户su - dmdba1.2 进入达梦数据库安装路径的bin目录,执行导库操作 导出语句:./dexp cwy_init/[email protected]:5236 file=cwy_init.dmp log=cwy_init_exp.log 注释: cwy_init/init_123..._达梦数据库导入导出

js引入kindeditor富文本编辑器的使用_kindeditor.js-程序员宅基地

文章浏览阅读1.9k次。1. 在官网上下载KindEditor文件,可以删掉不需要要到的jsp,asp,asp.net和php文件夹。接着把文件夹放到项目文件目录下。2. 修改html文件,在页面引入js文件:<script type="text/javascript" src="./kindeditor/kindeditor-all.js"></script><script type="text/javascript" src="./kindeditor/lang/zh-CN.js"_kindeditor.js

STM32学习过程记录11——基于STM32G431CBU6硬件SPI+DMA的高效WS2812B控制方法-程序员宅基地

文章浏览阅读2.3k次,点赞6次,收藏14次。SPI的详情简介不必赘述。假设我们通过SPI发送0xAA,我们的数据线就会变为10101010,通过修改不同的内容,即可修改SPI中0和1的持续时间。比如0xF0即为前半周期为高电平,后半周期为低电平的状态。在SPI的通信模式中,CPHA配置会影响该实验,下图展示了不同采样位置的SPI时序图[1]。CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出。_stm32g431cbu6

计算机网络-数据链路层_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输-程序员宅基地

文章浏览阅读1.2k次,点赞2次,收藏8次。数据链路层习题自测问题1.数据链路(即逻辑链路)与链路(即物理链路)有何区别?“电路接通了”与”数据链路接通了”的区别何在?2.数据链路层中的链路控制包括哪些功能?试讨论数据链路层做成可靠的链路层有哪些优点和缺点。3.网络适配器的作用是什么?网络适配器工作在哪一层?4.数据链路层的三个基本问题(帧定界、透明传输和差错检测)为什么都必须加以解决?5.如果在数据链路层不进行帧定界,会发生什么问题?6.PPP协议的主要特点是什么?为什么PPP不使用帧的编号?PPP适用于什么情况?为什么PPP协议不_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输

软件测试工程师移民加拿大_无证移民,未受过软件工程师的教育(第1部分)-程序员宅基地

文章浏览阅读587次。软件测试工程师移民加拿大 无证移民,未受过软件工程师的教育(第1部分) (Undocumented Immigrant With No Education to Software Engineer(Part 1))Before I start, I want you to please bear with me on the way I write, I have very little gen...

随便推点

Thinkpad X250 secure boot failed 启动失败问题解决_安装完系统提示secureboot failure-程序员宅基地

文章浏览阅读304次。Thinkpad X250笔记本电脑,装的是FreeBSD,进入BIOS修改虚拟化配置(其后可能是误设置了安全开机),保存退出后系统无法启动,显示:secure boot failed ,把自己惊出一身冷汗,因为这台笔记本刚好还没开始做备份.....根据错误提示,到bios里面去找相关配置,在Security里面找到了Secure Boot选项,发现果然被设置为Enabled,将其修改为Disabled ,再开机,终于正常启动了。_安装完系统提示secureboot failure

C++如何做字符串分割(5种方法)_c++ 字符串分割-程序员宅基地

文章浏览阅读10w+次,点赞93次,收藏352次。1、用strtok函数进行字符串分割原型: char *strtok(char *str, const char *delim);功能:分解字符串为一组字符串。参数说明:str为要分解的字符串,delim为分隔符字符串。返回值:从str开头开始的一个个被分割的串。当没有被分割的串时则返回NULL。其它:strtok函数线程不安全,可以使用strtok_r替代。示例://借助strtok实现split#include <string.h>#include <stdio.h&_c++ 字符串分割

2013第四届蓝桥杯 C/C++本科A组 真题答案解析_2013年第四届c a组蓝桥杯省赛真题解答-程序员宅基地

文章浏览阅读2.3k次。1 .高斯日记 大数学家高斯有个好习惯:无论如何都要记日记。他的日记有个与众不同的地方,他从不注明年月日,而是用一个整数代替,比如:4210后来人们知道,那个整数就是日期,它表示那一天是高斯出生后的第几天。这或许也是个好习惯,它时时刻刻提醒着主人:日子又过去一天,还有多少时光可以用于浪费呢?高斯出生于:1777年4月30日。在高斯发现的一个重要定理的日记_2013年第四届c a组蓝桥杯省赛真题解答

基于供需算法优化的核极限学习机(KELM)分类算法-程序员宅基地

文章浏览阅读851次,点赞17次,收藏22次。摘要:本文利用供需算法对核极限学习机(KELM)进行优化,并用于分类。

metasploitable2渗透测试_metasploitable2怎么进入-程序员宅基地

文章浏览阅读1.1k次。一、系统弱密码登录1、在kali上执行命令行telnet 192.168.26.1292、Login和password都输入msfadmin3、登录成功,进入系统4、测试如下:二、MySQL弱密码登录:1、在kali上执行mysql –h 192.168.26.129 –u root2、登录成功,进入MySQL系统3、测试效果:三、PostgreSQL弱密码登录1、在Kali上执行psql -h 192.168.26.129 –U post..._metasploitable2怎么进入

Python学习之路:从入门到精通的指南_python人工智能开发从入门到精通pdf-程序员宅基地

文章浏览阅读257次。本文将为初学者提供Python学习的详细指南,从Python的历史、基础语法和数据类型到面向对象编程、模块和库的使用。通过本文,您将能够掌握Python编程的核心概念,为今后的编程学习和实践打下坚实基础。_python人工智能开发从入门到精通pdf