数字后端基本概念-合集_corner test 后端-程序员宅基地

个人将基本概念重新整理

原碎片来源:Tao_ZT

个人空间 https: //blog.csdn.net/Tao_ZT

数字后端基本概念

macro

macro

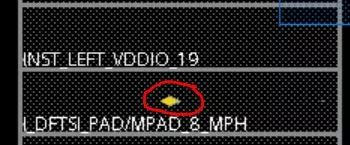

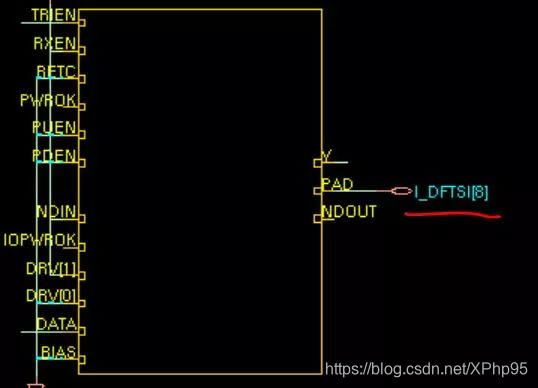

Macro,中文名宏单元。这是设计中最常见的一个单元了,Macro是一个宽泛的概念,通常我们把它分为硬核(Hard Macro)和软核(Soft Macro)。硬核就是我们最常见的Hard Marco,包括Memory,PLL等各种IP,他的逻辑在自己本身内部已经集成好,对于core本来来说并不可见。而软核就是包含逻辑的一层hierarchy,通常是place&route好的partition。下图就是一个常见的hard macro。

Macro有他自己单独的lef,里面会定义它的形状以及pin的位置等等信息。

MACRO PLLCLK

CLASS BLOCK ;

FOREIGN PLLCLK 0 0 ;

ORIGIN 0 0 ;

SIZE 300.00 BY 280.00 ; Macro形状

SYMMETRY X Y R90 ;

PIN ib

DIRECTION INPUT ;

USE SIGNAL ;

PORT

LAYER Metal1 ;

RECT 0.00 181.00 0.30 182.00 ; Macro Pin位置

END

END ibias

PIN clk

DIRECTION INPUT ;

USE SIGNAL ;

Macro的位置,我们在布局规划介绍会决定,通常这是很重要的一个步骤,Macro的位子决定了设计时序的收敛与否。

Box

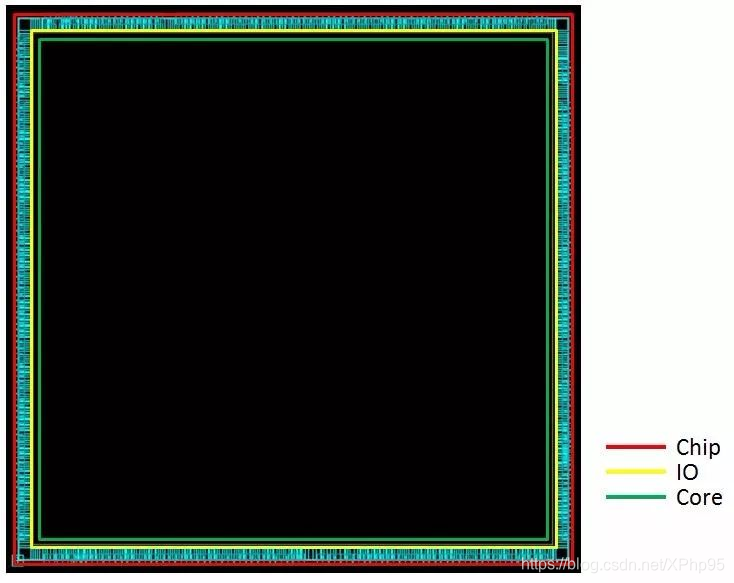

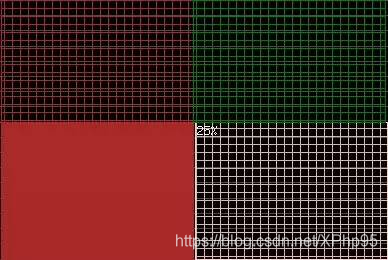

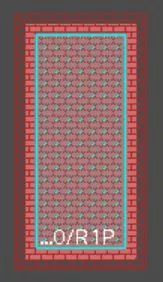

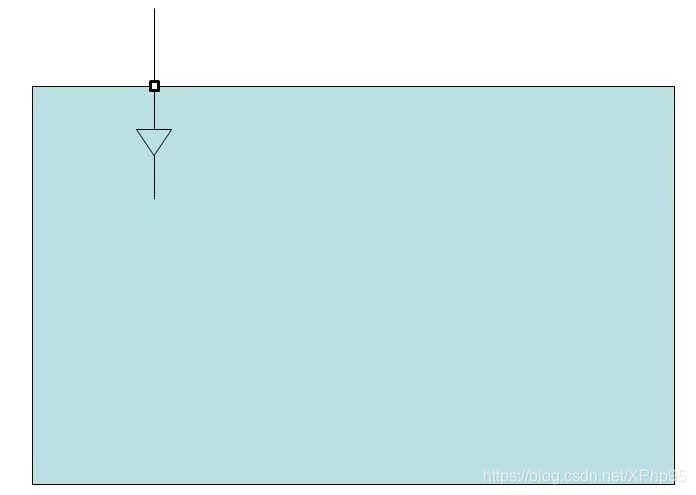

Box, 我们在做design planning的第一步就是确定floorplan的box,也就是设计的区域。这个区域可以划分为三个边界,如下图所示:

上图中,按对应的颜色框框可以分为:Die Box,IO Box,Core Box.

红色框,也就是最外面一圈,我们称为Die Box,也就是用来放置IO单元,包括Pad,Io Filler等

绿色框,也就是最里面一圈,我们称之为Core Box。是整块芯片的核心区域,放置std cell,hard macro等功能单元.

黄色框,就是io pad内部与core box之间的margin称为IO box, 它并没有任何实际限制,在不违反物理规则的情况下,很多Pad也可以伸进core area.

坐标

在后端软件中,我们用到最多的就是生成一个box,比如创建一个blockage,定义芯片的形状等。所以,学会通过坐标来表示一个box是最基本的知识点。

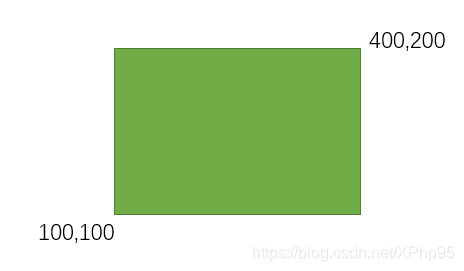

Rectangle Box: 首先我们来介绍的是最简单的矩形Box的坐标定义方法。对于这种Box,我们只需要记住Box左下角(llx,lly)和右上角(urx,ury)的两点坐标就行,下图中例子用坐标表示就是(100,100,400,200)

Rectilinear Box:对于不规则的图形的表示方法,就有点复杂了。分为两种,Box List和Polygon。

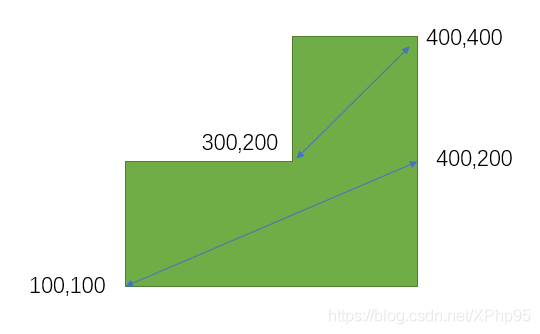

Box List:所谓Box List,是把一个不规则图形分成两个规则的矩形,分别记录两个图形的左下角和右上角坐标,就能表达出这个图形了。

下图例子用坐标表示就是(100,100)(400,200)(300,200)(400,400)

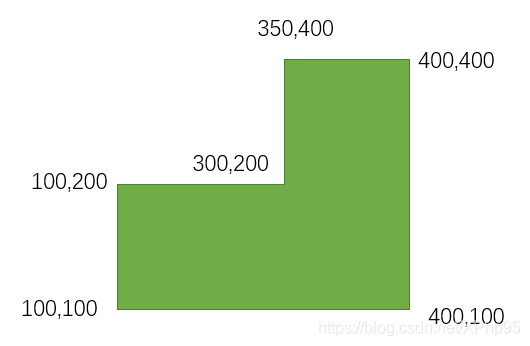

Polygon: BoxList只能支持简单的不规则图形,假如你需要画一个U字形或者T字形,这时你就需要采用Polygon了。在Polygon表示方法中,我们需要记录每个拐点的坐标,然后依次顺序写出来,用顺时针或者逆时针顺序都是可以的。如上图换成polygon形式表示就是:

(100,100)(100,200)(300,200)(350,400)(400,400)(400,100)

方向

方向的表示方法。在数字后端中,我们是如何去表征各个单元的方向的呢?

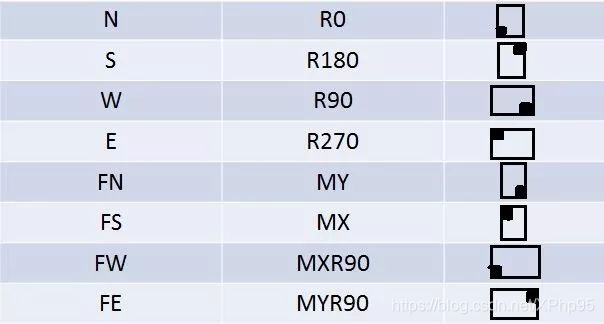

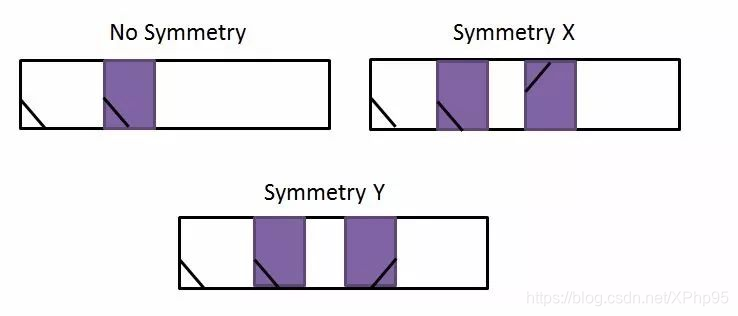

首先N,S,W,E就是大家熟悉的North, South, West, East. 另一种写法分别称为Rotate 0,Rotate 180,Rotate 90,Rotate 270。每个标准单元默认都放置于左下角,也就是R0位置,逆时针旋转90度就是R90位置,依次类推。

而FN,FS,FW,FE则代表Flip North,Flip South,Flip West, Flip East,表示反转以后的方向,对应着Mirror Y(沿Y轴翻转),Mirror X(沿X轴翻转),Mirror XR90,Mirror YR90。

standard cell

Standard cell,中文名标准单元。这是设计中最基本的逻辑单元了,是基本门和简单逻辑电路。我们平时常用的buffer, inverter, register等都属于标准单元。

standard cell的时序信息记录在.lib文件中

cell (INVX12_CSC28SL) {

area : 0.86528;

cell_footprint : “inv”;

threshold_voltage_group : “LVT”;

pg_pin (VDD) {

pg_type : primary_power;

voltage_name : “VDD”;

}

…

物理信息记录在lef文件中,

MACRO INVX12_CSC28SL

CLASS CORE ;

ORIGIN 0 0 ;

FOREIGN 0 0 ;

SIZE 1.26 BY 0.64 ;

SYMMETRY X Y ;

SITE unit ;

PIN VDD

DIRECTION INOUT ;

USE POWER ;

SHAPE ABUTMENT ;

PORT

LAYER M1 ;

RECT -0.052 0.6 1.612 0.68 ;

。。。

standard cell在netlist中完成例化,INVX12_F_CSC28SL是cell名字,U28是例化以后的名字。

INVX12_F_CSC28SL U28(

.Z(n21), .A(n24)

);

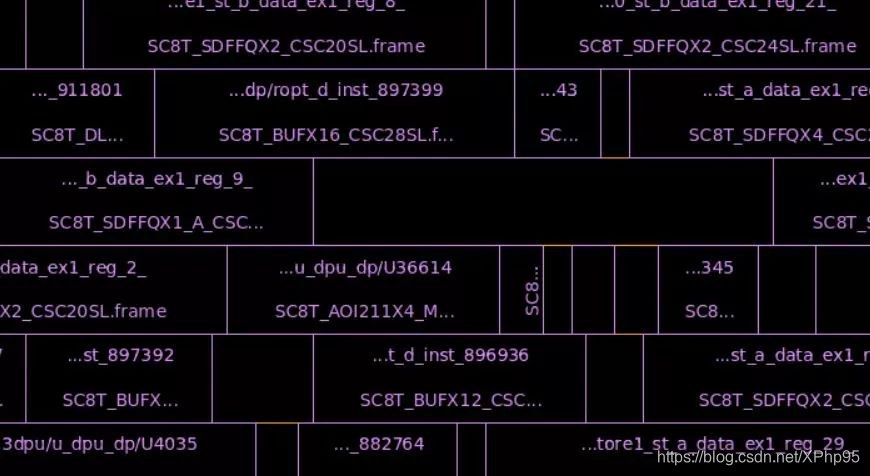

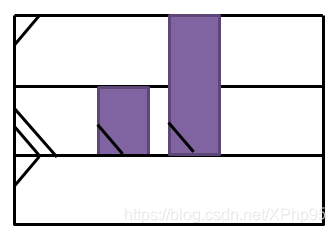

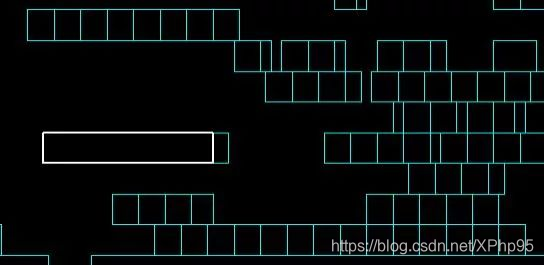

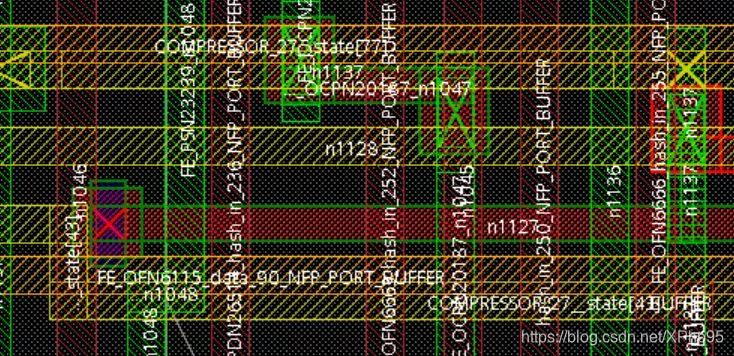

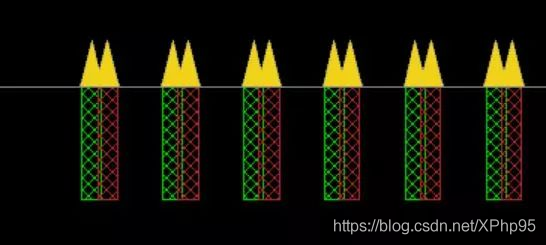

下图就是stardand cell在软件中的样子。他们被安放在row上

EndCap

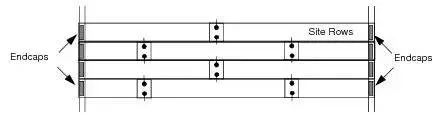

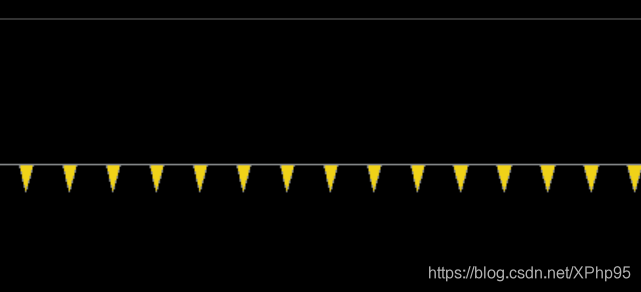

今天要介绍的数字后端基本概念是boundary cell,也被称为endcap Cell。Endcap是一种特殊的标准单元。在后端物理设计中,除了与,非,或等一些常见的标准单元外,还有一些特殊的物理单元(physical cell),它们通常没有逻辑电路,不存在与netlist当中,但是对整个芯片的运行,稳定却起着举足轻重的作用。那endcap cell就是其中一种,它俗称为拐角单元,作用是确保每个nwell都是nwell enclosed,类似一个封闭环。主要加在row的结尾(两边都要加) , 以及memory 或者其他block的周围包边,如下图所示:

使用方法:

命令

create_boundary_cells

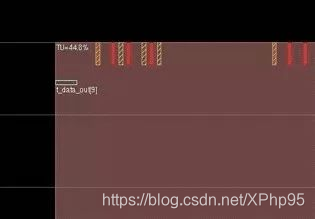

使用前需要指定放在left_boundary,right_boundary,top_boundary,bottom_boundary等cell,可以查询所用工艺库的工艺手册,如下图所示:

create_boundary_cells \

-left_boundary_cell $left_boundary_cell \-right_boundary_cell $right_boundary_cell \ -top_boundary_cells $top_boundary_cells \ -bottom_boundary_cells $bottom_boundary_cells \ -top_right_outside_corner_cell $top_XXX_cell \ -top_left_outside_corner_cell $top_XXX_cell \ -bottom_right_outside_corner_cell $bottom_XXX_cell \ -bottom_left_outside_corner_cell $bottom_XXX_cell \ -bottom_left_inside_corner_cells $bottom_XXX_cells \ -bottom_right_inside_corner_cell $bottom_XXX_cell \ -top_left_inside_corner_cell $top_XXX_cell \ -top_right_inside_corner_cell $top_XXX_cell \ -prefix "ENDFILL" \ -separator "_"

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

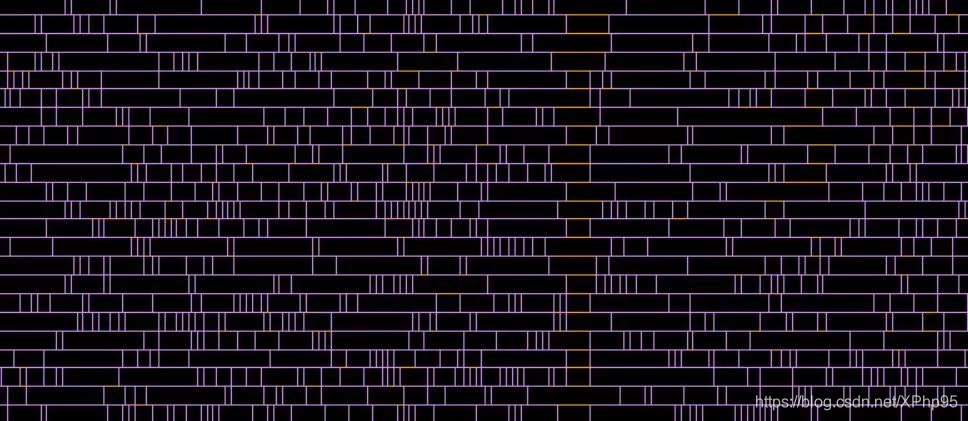

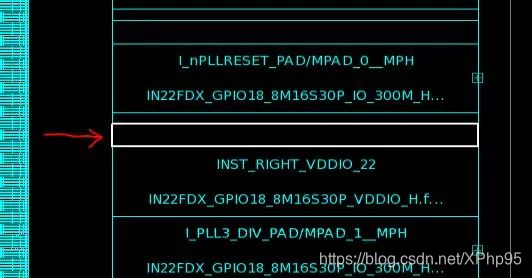

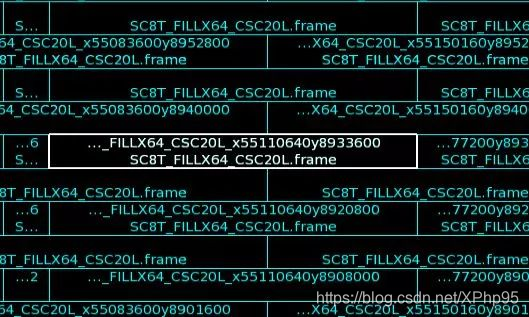

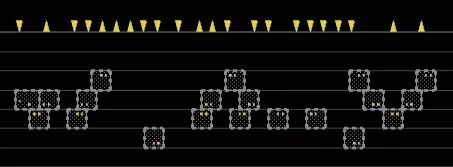

Welltap

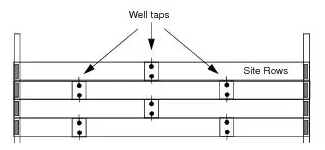

Tap cell, 也被称为welltap cell。这也是一种特殊的物理单元。 welltap是只包含well contact的cell,将衬底接到电源和地网络,避免衬底悬浮。主要防止CMOS器件的寄生闩锁效应(latch-up)

一般tap cell的作用范围是30~40um, 即每隔60um左右放置一个tap cell,具体的数据要参考工艺商给的document

well tap cell一般交错摆放,类似棋盘分布。如下图所示:

使用方法

命令

create_tap_cells

例: set tap_cell [get_lib_cell */SC8T_TAPZBX7_CSC28SL]

create_tap_cells \

-lib_cell $tap_cell \

-pattern stagger \

-distance 60 \

-offset 15 \

-prefix “WELLTAP” \

-separator “_” \

-skip_fixed_cells

black box

BlackBox, 中文名大家肯定很熟悉——黑盒子。在物理设计中,BlackBox类似于一个Hard Macro,它内部的东西完全看不见,只是一个黑盒子,但是它又类似于一个Module Boundary。 它可以被改变形状,而且它可以被分配pin和被分割出去(partition)。如下图所示,灰色的形状就是Black Box。

那BlackBox 有什么作用呢?其实BlackBox是一种较为粗糙的模型,由于它看不见里面的东西,这样的结构使得它做任何implementation速度都很快,取而代之的精准度就会相对较低。

使用方法:

命令:

create_blackbox u0 -boundary { {50 50} {200 200}}

row

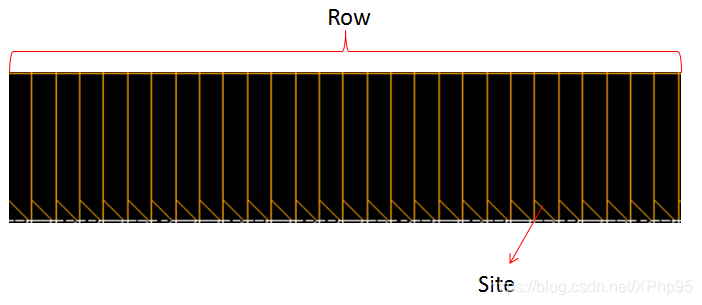

Row。我们知道row是表征Floorplan横向排列的一个重要网格,可以将它解释为“排”,它对std cell的摆放起着限制约束作用。Row是placement的基础,因为需要摆放std cell的地方,就必须要首先创建row。下面我们来介绍下Row的各个内容和属性。

Row是由SITE组成的。SITE定义的是最小的布局单位。如下图所示

我们可以在Lef中找到Site定义:

SITE unit_8t site名字

CLASS CORE ; site类别

SYMMETRY X Y ; site方向

SIZE 0.100 BY 0.640 ; site宽度,高度

END unit_8t

SITE的类别通常分为core和pad,分别对应着std cell的row和io cell的row。SITE的方向通常有X,Y,R90三个参数。X代表可以沿X轴翻转,Y代表可以沿Y轴翻转,R90代表可以任意翻转。SIZE定义了site的宽度,通常std cell都是site的整数倍高度,宽度。

有了SITE定义以后,我们就可以生成最基本的row了,如下图所示:

Row也有自己的方向,如上图箭头所示,通常相邻的row会相互abut并且flip,这样相邻site可以共用一根电源线,节省Power资源。

所有std cell都必须snap到row上面,这是最基本的place规则。

默认的std cell摆放方向遵从Row的方向,即方向箭头一致,但是根据cell本身的symmetry,std cell的摆放位置也可以有如下选择:

这是最常见的row,实际design中,我们还能经常见到一些其他种类的row。

常见的有double height,trible height的row,用来摆放两倍高,三倍高的cell。

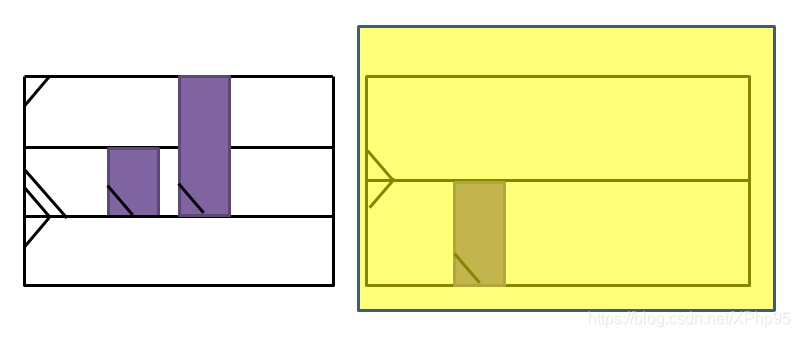

这边值得注意的是,一般我们只允许创建整数倍高的row,而在Voltage island中,我们允许创建非整数倍高的Row,比如默认电压区域用的是9T单元,而在Voltage island中我们使用了12T的cell,这时候就需要创建非整数倍高度的row。如下图所示

Row这栏就是和Row相关的一些信息。

Standcell Row:显示core里面的row。

IO Row就是IO区域的Row。

Row Pattern:显示具体组成row的site。

Macro pattern:显示macro的site显示,这个没怎么用过。

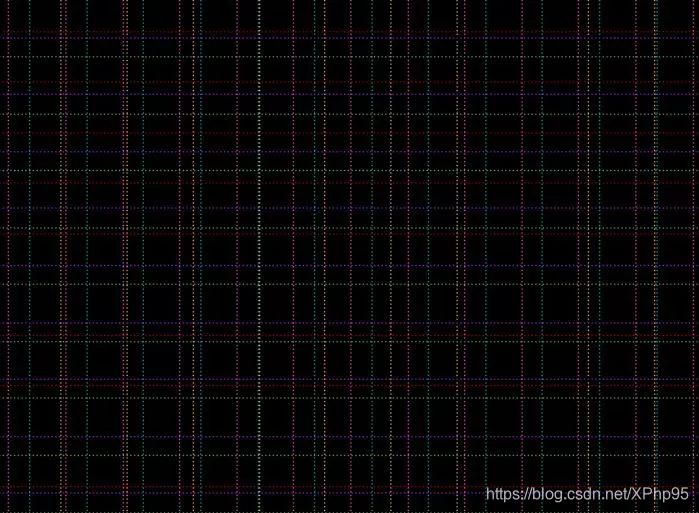

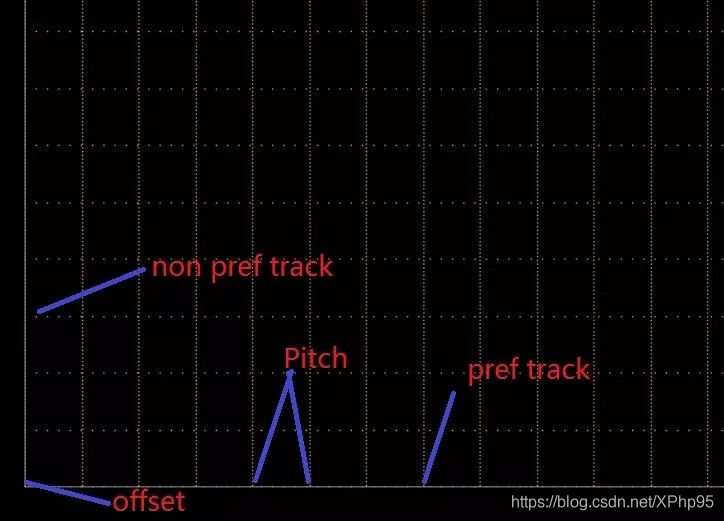

track

Track是指走线轨道,和row一样,可以约束走线器的走线方向。信号线通常必须走在track上。Std Cell的高度通常用metal2 track pitch来表示,常用的 std cell 库有 7T /9T /12T,就是以 track 来区分的, 9T 就是说 std cell 的高度范围内可以走九条线,所以一般来讲, 7T cell 的 size 最小, 9T cell 的 size 稍大。

下图中五颜六色的线条就是每层layer上定义的track走线轨道

通常我们在design的technology lef中定义Track的属性,如下图所示:

LAYER M1

TYPE ROUTING ;

DIRECTION VERTICAL ;

PITCH 0.090 0.064;

OFFSET 0.000 0.000;

MAXWIDTH 2 ;

WIDTH 0.032 ;

上述M1 layer的定义中,TYPE ROUTING代表这是一层走线层,我们还有其他的type包括Implant,Masterslice等。

DIRECTION代表这层Metal prefer走线方向,这边值得注意的是,每层track会分为pref track和non pref track。pref track就是这层layer上主流的走线方向,那剩下的non pref track就是非主流方向。因此上述例子中的主流走线方向就是vertical(纵向),非主流就是横向(honrizontal)。通常。走non-pref track的wire会比较宽,这样就比较占用绕线资源。所以,一般不推荐使用non-pref track。特别是在先进工艺的设计中,绕线资源极其紧张,一般很少用到non-pref track.

PITCH就是每条track之间的间距,上述例子中,垂直方向间距是0.09,水平方向是0.064.

OFFSET就是第一条track偏离起始点的距离

WIDTH就代表默认这层layer上wire的宽度,MAXWIDTH就代表最高不能超过多少width

Filler

Filler cell,通常是单元库中与逻辑无关的填充物,可以分为IO filler以及普通的standard cell filler。

IO filler,也叫作pad filler,通常是用来填充I/O 单元与I/O单元之间的空隙。为了更好的完成power ring,也就是ESD之间的电源连接。通常是在Floorplan阶段时添加。

使用方法:

create_io_filler_cells

create_io_filler_cells -reference_cells FILLER

standard cell filler,也是为了填充std cell之间的空隙。主要是把扩散层连接起来满足DRC规则和设计需求,并形成power rails。这个在route之前,之后加都可以。

使用方法:

create_stdcell_fillers

create_stdcell_fillers \

-lib_cells {mylib/FILL_2X mylib/FILL_1X}

Decap

Decap cell。 中文名,去耦单元,这是一种特殊的Filler cell。当电路中大量单元同时翻转时会导致冲放电瞬间电流增大,使得电路动态供电电压下降或地线电压升高,引起动态电压降,俗称IR-drop。为了避免IR-drop对电路性能的影响,通常在电源和地线之间放置由MOS管构成的电容,这种电容被称为去耦电容或者去耦单元,它的作用是在瞬态电流增大,电压下降时向电路补充电流以保持电源和地线之间的电压稳定,防止电源线的电压降和地线电压的升高。

使用方法

create_stdcell_fillers

需要注意的是Decap cell是带有metal层的,为了不影响工具routing resource,一般建议是最后routing全部结束后再加,加完之后再添加普通的不带metal的filler.

Grid

Litho Grid

Litho Grid,中文名,光刻格点。又被称为制造单元格点,这是最基本的网格单元,任何元件都要对Litho Grid上,不然就无法被制造,它定义在design的technology LEF(最前面几行)中。如:

MANUFACTURINGGRID 0.001 ;

这就代表着改设计的制造单元格点间距为0.001, 起始点是Die Box的lower left角上,如下图所示:

这个实际用处不大,一般工具也不会出现不在Litho Grid的情况

FinFET Grid

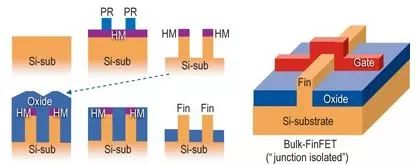

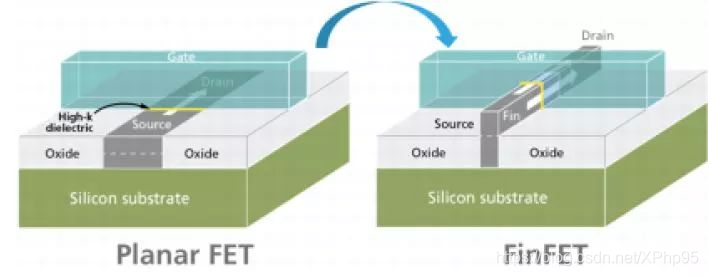

FinFET Grid,它也是一种设计格点。介绍该格点前,我们首先来了解一下什么是FinFET技术。

FinFET称为鳍式场效晶体管(Fin Field-Effect Transistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。FinFET源自于传统标准的晶体管—场效晶体管 (Field-Effect Transistor; FET )的一项创新设计。在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。在FinFET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。

简单来说,是一种新型的3D多闸道晶体管,采用FinFet技术设计,可以大大地提高芯片处理速度以及大幅度降低功耗,这在当今注重低功耗设计的手机芯片中尤为重要,FinFet技术是推动芯片技术走向16/14nm的重要节点。

了解了FinFet技术概念后,我们再来看下FinFet grid概念,这是对应于Floorplan中对应于FinFet引入的网格单元,在FinFet设计中,所有元件(包括macro)都要对齐到FinFet grid上, 它的定义在technology LEF中:

PROPERTYDEFINITIONS

LIBRARY LEF58_FINFETSTRING "

VERTICAL HORIZONTAL 的关键字分别对应了X/Y轴的pitch

是不是感觉和前文说的那些高端概念并什么太大关系?其实后端工具已经把这些复杂技术简单化的体现在软件中的应用里了

Blockage

Obstruct:显示hard和soft blockage。

Area Density:显示partial blockage.

Macro blkg:显示macro-only blockage

Routing blkg:显示普通的routing blockage.

Fill blkg:显示metal fill的blockage

trim blockage:显示trim metal上的blockage(在7nm Advance node上,wire终点需要trim metal相连)。下图中右边wire的两端就是trim metal.左边的blockage就是trim metal blockage

Placement Blockage

Placement Blockage. Placement blockage是大家在floorplan时经常用的一种人为约束。可以有效控制区域的density。从而避免congestion的问题,提高routing的效率。

Placement blockage的类型很多,一共分为9种,分别对应hard, hard_macro, soft, partial, category, rp_group,allow_buffer_only,allow_rp_only,register

hard: 是约束最严格的blockage,该区域范围内,place,legalize, optimize,CTS等任何阶段都不能摆放instance。

hard blockage

hard_macro: 该区域内不允许摆放hard macro,在自动macro placement阶段工具不会摆放macro在该区域。

hard macro blockage

soft:该区域内,在placement阶段不允许摆放instance,但是在legalize,optimize阶段时允许摆放instance的

soft blockage

partial: 如果要使用partial blockage,首先要人为设计一个阻碍百分比值。在该区域内,工具会block住阻碍值的instance。如果设定了block百分比值是40%,就说明该区域至少会block40%的instance,也就是说该区域最多允许摆放60%的instance. 值得注意的是partial blockage也是只在placement阶段起作用,在legalize,optimize阶段时都不起作用。

partial blockage

category: 这是一种特殊的partial blockage,在某些区域,如果我们不想摆放某种指定的instance,可以把这些instance都指定为一个category,然后category blockage下面的区域就不会摆放这些instance

category blockage

rp_group: 这也是一种特殊的partial blockage,rp_group blockage的区域不允许摆放relative placement instance,很少用到,如果有用relative placement flow的童鞋可能会用到。

rp_group blockage

allow_buffer_only: 这也是一种特殊的partial blockage, 该blockage区域只允许摆放buffer,当然也是只在placement阶段起作用,在legalize,optimize阶段时都不起作用。

allow_buffer_only blockage

allow_rp_only:这也是一种特殊的partial blockage, 该blockage区域只允许摆放relative placement group,不过hard macro依然可以摆放。

allow_rp_only blockage

register:这也是一种特殊的partial blockage, 该blockage区域不允许摆放register,当然也是只在placement阶段起作用,在legalize,optimize阶段时都不起作用。

图形界面

Create Placement Blockage键

功能非常简单,创建一个Placement blockage。快捷键是Shift+Y。

Placement blockage是大家在floorplan时经常用的一种人为约束。可以有效控制区域的density。从而避免congestion的问题,提高routing的效率。

其实在Innovus中,一共有4种placement blockage, 对应的type分别是hard, soft, partial, Macro_Only。

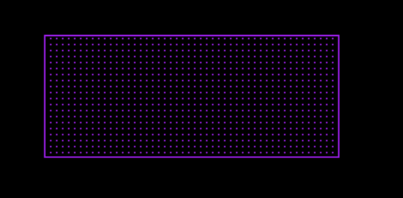

Hard:打hard blockage的区域,在设计的任何阶段都不能摆任何block和cell。对应着下图的左下角。

Soft:打soft blockage的区域,在placement阶段不能摆standard cell. 但是在place opt, CTS, ECO place, place legalization时可以被place。对应下图的左上角。

Partial:打partial blockage的区域,需人为设定一个百分比值,而在place之后,该区域的place density不能超过设定的百分比。对应着下图的右下角。

Macro_Only: 打macro_only blockage的区域,不允许Macro Placer摆放macro. 但是对standard cell来说, 可以任意摆放,相当于一个free area. 对应于下图右上角。

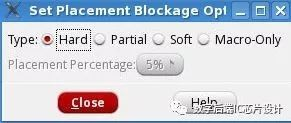

使用方法就是点一下这个键,然后在GUI上圈住想要打placement blockage的区域。点击F3出现如下设置界面。可以选择placement blockage的类型,以及partial blockage的密度。

注意:密度只能以5%递增。

register blockage

Routing Blockage

routing blockage(绕线阻碍物)。这个概念很简单,就是给某些金属加上blockage属性,让工具走线时不通过该区域。

可以使用命令create_routing_blockage创建

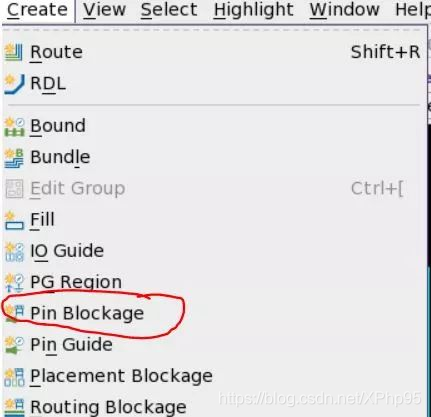

PinBlockage

Pin Blockage(引脚阻碍物)。这是一种pin constraint,用于Pin assignment中。从名字中大家也能理解,带有pin blockage的区域,place pin时,不会将pin打在该区域。

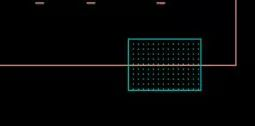

需要注意的是Pin blockage只能打在module boundary的边界。下图中绿色部分就是pin blockage。该区域内,不允许放置pin。

使用方法:

命令:

create_pin_blockage -boundary { {100 100} {200 200}} -layers {M1 M2}

GUI

keep out margin

今天我们要介绍的数字后端基本概念是Keepout Margin(避开圈)。 这也是blockage的一种,只是比较特殊,它会随着cell一起移动,有点类似覆盖在这个cell上,在这个光圈内的区域不能放置其他单元。当几个Macro之间有congestion问题时,可以添加一些Keepout Margin,阻碍buffer, inverter的插入。下图中的外面一圈就是Keepout Margin。我们可以添加的Keepout Margin的种类有很多,我们可以添加hard placement blockage, soft placement blockage, route blockage等。

hard: 是约束最严格的blockage,该区域范围内,place,legalize, optimize,CTS等任何阶段都不能摆放instance。

soft:该区域内,在placement阶段不允许摆放instance,但是在legalize,optimize阶段时允许摆放instance的。

使用方法:

命令:

create_keepout_margin -type hard -outer {10 10 10 10} [get_cells RAM1]

size blockage

Size Blockage,中文名称是扩散阻碍物。这个blockage大家很少看到。Size Blockage形状如下:(紫色)

相对于其他blockage,这个blockage的使用频率很低。用处也不大,它可以阻止resize line穿过Size Blockage。换而言之,在做resize Floorplan时,被Size Blockage覆盖住的地方不会被resize,macro的相对位置会被keep住。但这只对自动resize Floorplan时有用,对于手动画resize line的方式,相对位置无法被keep住。

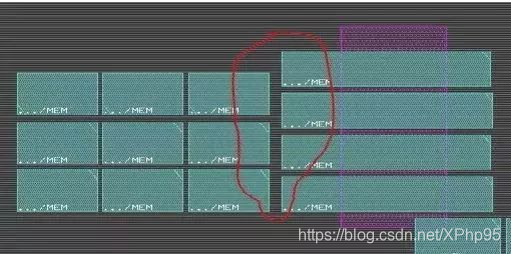

对照上下两图,当做了resize Floorplan将design的沿X方向扩大100um以后,Size blockage覆盖住的区域(红圈处),macro之间的相对位置不会变。

使用方法

addSizeBlockage

addSizeBlockage -name sBlkg1 -box 200 200 400 400

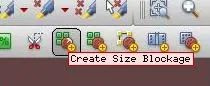

GUI图形界面

mode

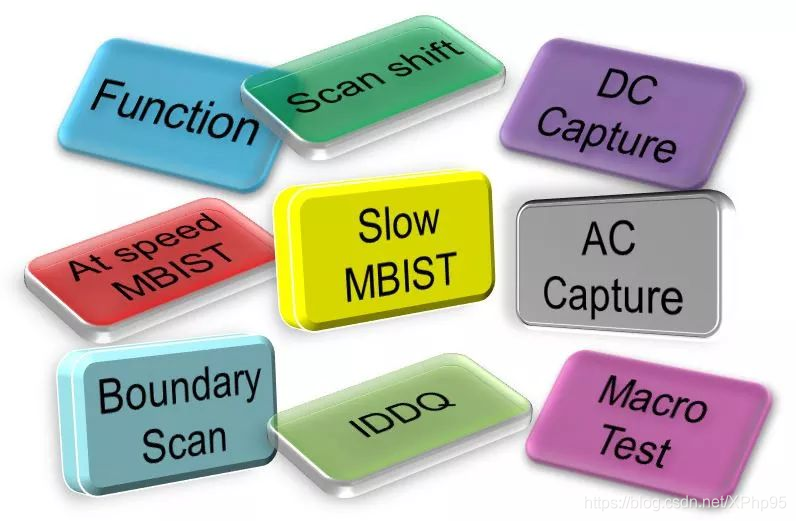

今天要介绍的时序基本概念是Mode(模式). 这是Multiple Scenario环境下Sign off的一个重要概念。芯片的设计模式包括最基本的功能function模式,以及各种各样相关的测试模式。

PD的同学应该比较熟悉Function, Scan Shift, Capture, ASST这些模式。其实如果细分,这些还能划分出好多新的模式,如下图所示。这些名词可能你经常看见,但是你知道他们具体检测啥,有啥作用嘛?下面我就来分别简单介绍下这些模式。

Function

这个模式不用过多介绍,就是大家最常见的功能要求模式,即标准时序约束模式。

Scan Shift

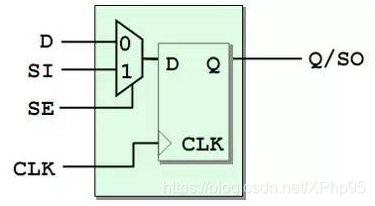

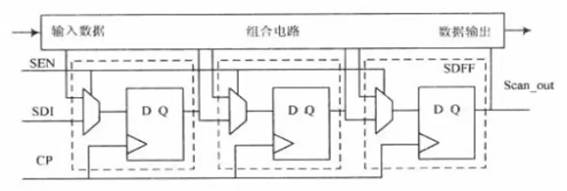

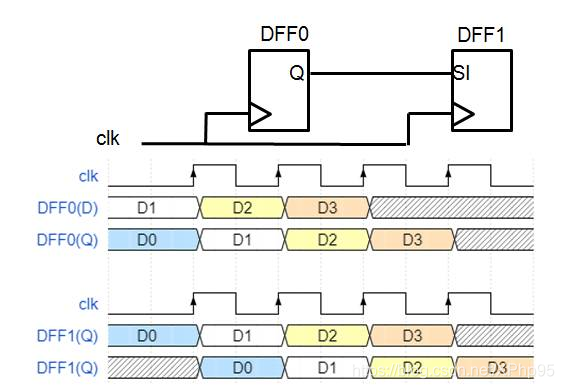

这个模式大家也很熟悉,移位扫描模式。先介绍下基本的Scan chain概念:由于芯片内部是一个黑盒子,在外部难以控制。我们将芯片中的所应用的普通寄存器替换成带有扫描功能的扫描寄存器,首尾相连成串,从而可以实现附加的测试功能,这就是Scan chain的概念。下图一就是扫描寄存器,下图二就是将扫描寄存器串起来的Scan Chain

因此,当Scan enable端接1,扫描寄存器工作在scan shift模式,把数据pattern移出来,通常这个模式下的时钟频率都很慢,一般就几十Mhz。如下图所示:

DC capture

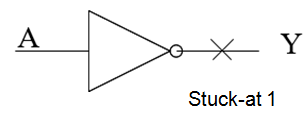

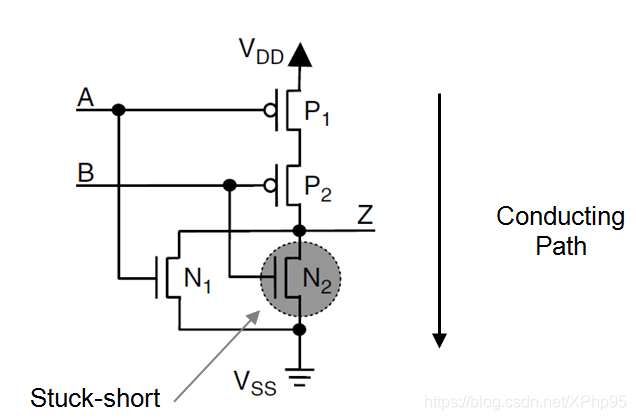

capture mode通常分为低速和高速模式,分别对应DC capture和AC capture. Capture模式下,Scan enable信号接0,扫描寄存器工作在正常模式下,这时候开始检查function上的pin连接。 低速DC capture也就是我们经常说的Stuck-at模式,主要检查我们平时常见的stuck-at 0/1错误。比如下图中的 inverter A端如果被接到了VSS端的话,就是一个stuck at 1的fault。

AC capture

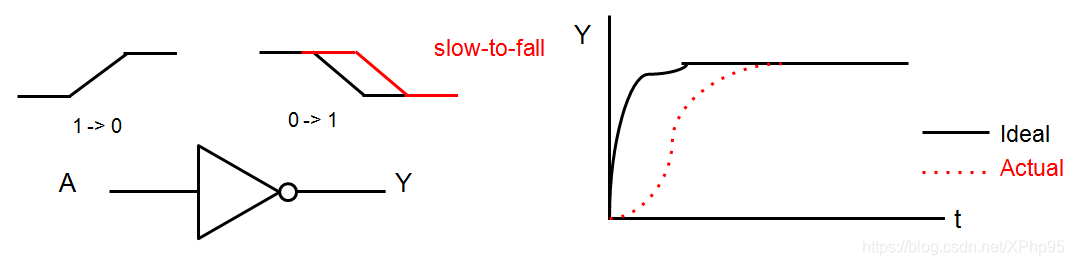

AC capture也被称为At-speed Structural Test(ASST),是一种高速测试模式,主要测试芯片中的延迟故障,也就是transition。随着半导体制造工艺的不断发展,片上器件的几何尺寸越来越小。此时,由于制造工艺异常,材料纯度不够,环境杂质等因素影响所造成的随机缺陷,导致电路中某些信号transition time变长,如果这种变化造成关键路径上的延迟不满足最大延迟要求,那么整个电路就不能工作在正常频率下。我们称这种故障为延迟故障。如下图的inverter,如果它下降的transition time延迟,就会导致它整个propagation delay超出理想限定的范围。

现在高性能超大规模的芯片的故障也越来越多地表现为延迟故障,而不是传统的stuck-at 故障。因此这个ASST模式也是很重要的,通常会单独作为一个模式定义在mcmm环境中。

At Speed MBIST

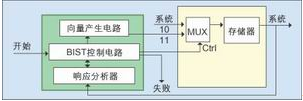

MBIST也分为高速和慢速,只不过一般都在高速下测试,慢速很少用到,高速模式下一般测试memory的读写功能。MBIST,全称Memory Built-In Self-Test。MBIST是面向嵌入式芯片存储器的测试方式,用于测试存储器工作是否正常。芯片内部有一个BIST Controller,用于产生存储器测试的各种模式和预期的结果,并比较存储器的读出结果和预期结果。

为什么需要MBIST?

在扫描链很长而且数量很多时,单芯片测试时间是很长的,而且高级测试仪器的价格也急速攀升,因此BIST技术就应运而生。

采用BIST技术的优点在于:降低测试成本、提高错误覆盖率、缩短测试时间、方便客户服务和独立测试。MBIST模式一般覆盖在function模式下面

Slow MBIST

低速Mbist, 一般情况下用不着,只做调试用,或者用于某些高速测不到的情况。

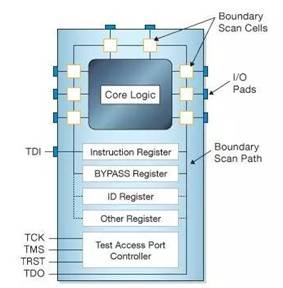

Boundary Scan

Boundary Scan,我们称之为边界扫描。是欧美一些大公司联合成立的一个组织——联合测试行动小组(JTAG),主要为了解决PCB板上芯片与芯片之间互连测试而提出的一种解决方案。边界扫描是在芯片的每一个输入输出引脚上增加一个存储单元,然后再将这些存储单元连成一个扫描通路,从而构成一条扫描链。由于这条扫描链分布在芯片边缘,因此被称为Boundary Scan。总之,该模式主要测试芯片IO上的信号,一般包含在function mode下面。

Macro Test

该模式下,主要测试一些Analog模块以及其他一些IP。

IDDQ

IDDQ全称 Integrated Circuit Quiescent Current,即静态电源电流,这是一种主要检测器件漏电的模式。IDDQ测试目的是测量逻辑状态验证时的静止(稳定不变)的电流,并与标准静态电流相比较以提升测试覆盖率。

IDDQ测试运行一组静态IDD测试的功能序列,在功能序列内部的各个独立的断点,进行6~12次独立的电流测量。测试序列的目标是,在每个断点验证总的IDD电流时,尽可能多地将内部逻辑门进行开-关的切换,toggle率尽可能高。 IDDQ测试能直接发现器件电路核心是否存在其他方法无法检测出的较小的损伤。

好了,Mode的介绍就到此为止了。我们平时的mcmm文件里并不会分得这么细,大部分Mode都会合并,一般最后剩下的只有function, scan shift, asst等几个主要的模式,其他的可以通过设置case值来切换。

bound

今天我们要介绍的数字后端基本概念是Placement Bound(布局约束)。Bound是一个约束的概念,用来控制placement的摆放,通常,在一个Bound区域里的standard cell会摆放得更近一些。个人感觉bound对timing的优化作用有限,有时候反而不如不用,因为很多standard cell并不是你想放的地方工具就觉得好。

Bound按照类型,可以分为move bound和group bound。move bound需要指定固定的区域,属于这个bound里面的standard cell会尽可能摆放在这个区域;而group bound没有固定的区域,它的位置会随着standard cell的移动而移动。

而这两种bound按照约束强弱,又可分为soft, hard, exclusive三种类型。

soft bound: 工具会尽可能将standard cell摆放到bound区域内,但也可能摆放到外面,可以认为该区域“可以进,可以出”

hard bound: 工具必须将standard cell摆放到bound区域内,但该区域可以摆放别的standard cell,可以认为该区域“可以进入,不可以出去”

exclusive bound: 工具必须将standard cell摆放到bound区域内,而且该区域不可以摆放别的standard cell,可以认为该区域“不可以进入,不可以出去”

使用方法:

命令:

move bound

create_bound -name movebound -boundary \

{ {100 100} {200 200}} [get_cells attr*]

group bound

create_bound -name groupbound \

[get_cells adder*]

GUI

dummy metal

今天我们要介绍的数字后端概念是Metal Fill,也被称为dummy metal。就像名字一样,它是一种dummy,没有实际的连线功能,只是为了满足Metal Density。 通常在最后route完之后添加。

使用方法:

signoff_create_metal_fill

prompt> signoff_create_metal_fill -mode add \

-coordinates { {100 150} {300 200}}

当然一般推荐在Calibre里面加会比较好~

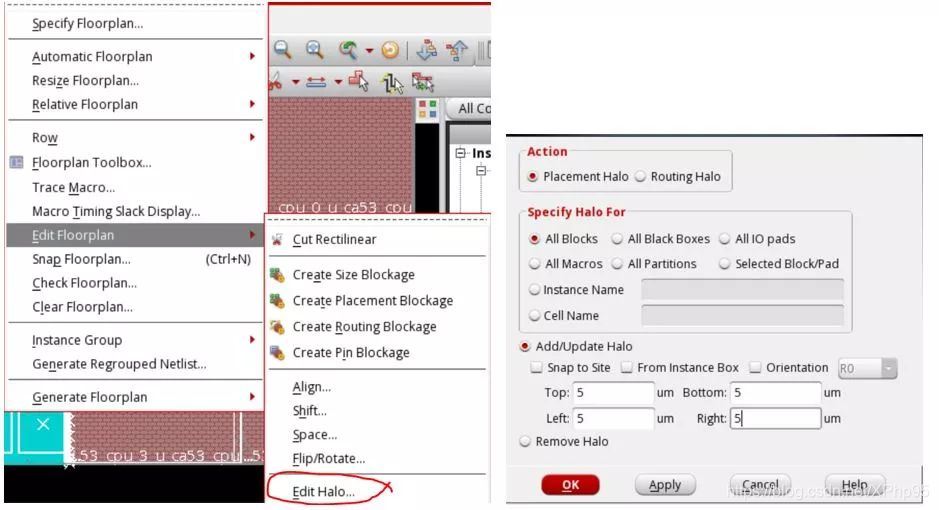

Halo

placement Halo

Placement Halo,布局晕环。这是大家在floorplan时经常用的一种人为约束。同样可以起到阻止摆放std cell的作用。和blockage有点类似,但是,用法有所区别。Halo是基于cell生长,可以跟着cell一起移动,而blockage则是基于area, 在两个macro之间congestion比较严重时候 可以在之间加入一些halo。如下图所示

使用方法

addHaloToBlock

addHaloToBlock -allBlock 5 5 5 5

GUI 图形界面

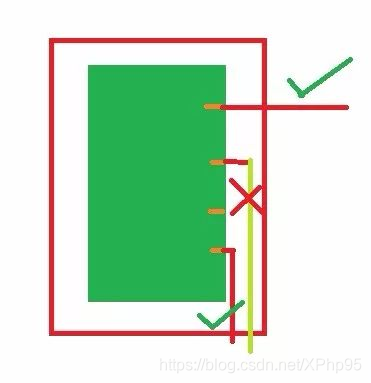

Route Halo,中文名绕线光晕。相比于我们经常使用的placement halo,Route Halo很少用到。其实它也是一种基于cell移动的Halo.如下图所示:

它的作用也是阻止信号线的走线,是为了防止SI的violation. 使用了Route halo以后,只有与边界正交,或者离pin很近的信号线才是允许的。 具体如下图所示:

使用方法

addRoutingHalo

addRoutingHalo -space 10 -top M7 -bottom M3 -allBlock

Net

Net。中文名线网,这个是最基本的概念了,对初学者来说,不要把它与wire混淆概念。Net是一个逻辑概念,存在于verilog语言中。线网用于对结构化器件之间的物理连线进行建模,描述器件之间的连线关系。如器件的管脚,模块的端口,与门或门的输入输出等等,都需要用线网来描述。

以一位全加器为例,所有与门、或门、异或门的输入输出都是线网类型的信号。线网类型的信号必须要有器件来驱动它的,否则线网信号的值为高阻(z)。线网信号不存储逻辑值,它代表的是物理连线,它的值随着驱动器件输出的变化而变化。

在Verilog HDL中,一共有11种类型的线网信号,分别是:wire、tri、wor、trior、wand、triand、trireg、tri1、tri0、supply0、supply1,其中最常用的就是wire型线网,在绝大部分设计中都可以只用wire来定义线网信号。

Wire

Wire。需要注意的是,后端工具里面的wire并不是指verilog网表里的wire线型。它是将net物理化的概念,每一条net在后端工具里面是由许多小段的wire组成,每一小段wire我们称之为wire segment.

wire按照类型可以分为Regular Wire(信号线),Special Wire(电源线),Patch Wire(补丁线)。

Regular Wire就是我们平常见到的信号连线,连接各个Signal Pin的金属线段。每层金属层上的Regular wire默认的宽度都是一样的。

Special Wire就是电源接地线,平常我们所见到的power ring,stripes,power rail等都是Special Wire。一般用高层金属走线。

Patch Wire,我们称之为补丁线。这是先进工艺中的一种走线,用于修复Min Area,Min Step等DRC,不属于任何net。

Pin

Pin,中文名叫做引脚。在一个设计中,Pin的种类分为好几种。

Instance Pin: 器件上的输入输出引脚,负责信号的传送

IO pin:模块的输入输出端口,也称为IO port。负责外部信号的传递输送

Physical Pin: Physical Pin是IO pin具体物理化的信息,该引脚用于底层模块与上层模块拼接时的接口,类似一个纽扣一样,定义模块走线的起点和终点。它也是有具体的金属层参数信息,和普通wire一样。

Partition Pin: 切分模块的引脚。用于在顶层模块未切分时,定义physical pin的位置,这个阶段的physical pin,我们称之为partition pin。和Physical Pin一样,他具有实际的金属层参数信息。

Port

Port。中文名端口,也被称为Terminal。负责信号的传输。

在芯片顶层,Port是信号输入点。如下图所示:

而在子模块设计层面,port也被称为IO pin,相当于I/O单元的作用。

IO buffer

IO Buffer。主要是指放置在block level的port附近的buffer,可以起到增强port的吸引力的作用, 提高一下驱动port的驱动能力,防止block外面wire太长,而使得计算delay不准。

使用方法

attachIOBuffer

attachIOBuffer -baseName iobuffer -in bufx4

Via

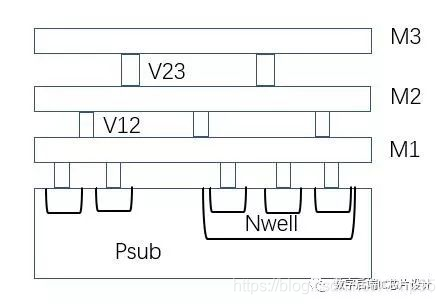

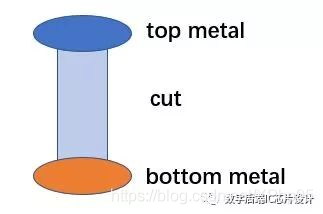

是Via。中文名称互连线通孔。我们知道,芯片的连线有不同层的金属互连线相互连接。而Via的作用就是连接这些不同层的金属。如下图所示:

一个完整的通孔是由三层组成的,包括两个互连层和一个cut层,cut层可以理解为连接两层互连线的接口。比如V23,就代表着Metal 3与Metal 2之间的Via,中间是cut层,Metal 3是它的top metal, Metal 2是它的bottom metal。如下图所示:

Via的种类也分好多种,按照功能划分,可以分成regular via(信号线通孔)和power via(电源线通孔)。这个很好理解,信号线之间的连接用regular via,通常比较小一点;电源线之间的连接使用power via,通常会大一点。

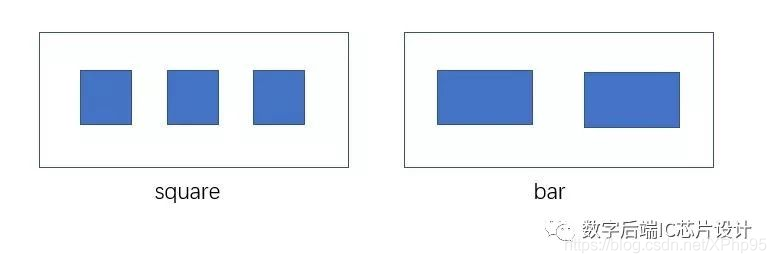

按照cut的形状,可以分为square(正方形)和bar(长方形)via,bar via拥有更大的cut面积,电阻可以更小一点。

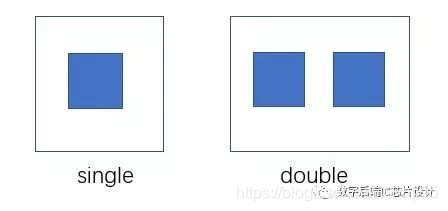

按照cut的数量,可以分为single cut(单孔)和double cut(双孔),面积允许的话,一般建议尽量选择双孔的Via,电阻会较小。

飞线

是Flighline。中文名称是飞线。这是图形界面上查看连接关系非常实用的一个功能,主要是用于显示各个object之间的连接关系。

这种连接关系主要包括显示pin与pin之间的连接,macro与macro之间,module与module之间以及macro和instance属于哪个module。如下图所示:

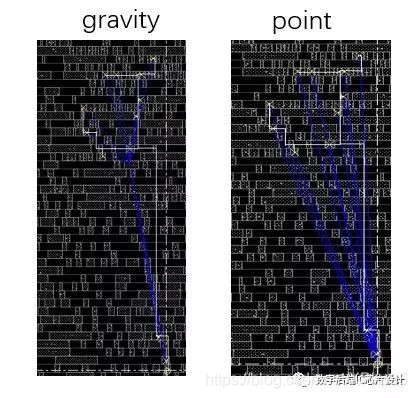

一般地,我们有两种显示flightline的方式,第一种是通过gravity风格,是默认的方式,会在几条线中间取一个重心点,另一种方式是显示所有点对点的连线,需要勾选setting=> Flightline => Show Flightline From Output pin

原碎片来源:Tao_ZT

https://blog.csdn.net/Tao_ZT

智能推荐

JWT(Json Web Token)实现无状态登录_无状态token登录-程序员宅基地

文章浏览阅读685次。1.1.什么是有状态?有状态服务,即服务端需要记录每次会话的客户端信息,从而识别客户端身份,根据用户身份进行请求的处理,典型的设计如tomcat中的session。例如登录:用户登录后,我们把登录者的信息保存在服务端session中,并且给用户一个cookie值,记录对应的session。然后下次请求,用户携带cookie值来,我们就能识别到对应session,从而找到用户的信息。缺点是什么?服务端保存大量数据,增加服务端压力 服务端保存用户状态,无法进行水平扩展 客户端请求依赖服务.._无状态token登录

SDUT OJ逆置正整数-程序员宅基地

文章浏览阅读293次。SDUT OnlineJudge#include<iostream>using namespace std;int main(){int a,b,c,d;cin>>a;b=a%10;c=a/10%10;d=a/100%10;int key[3];key[0]=b;key[1]=c;key[2]=d;for(int i = 0;i<3;i++){ if(key[i]!=0) { cout<<key[i.

年终奖盲区_年终奖盲区表-程序员宅基地

文章浏览阅读2.2k次。年终奖采用的平均每月的收入来评定缴税级数的,速算扣除数也按照月份计算出来,但是最终减去的也是一个月的速算扣除数。为什么这么做呢,这样的收的税更多啊,年终也是一个月的收入,凭什么减去12*速算扣除数了?这个霸道(不要脸)的说法,我们只能合理避免的这些跨级的区域了,那具体是那些区域呢?可以参考下面的表格:年终奖一列标红的一对便是盲区的上下线,发放年终奖的数额一定一定要避免这个区域,不然公司多花了钱..._年终奖盲区表

matlab 提取struct结构体中某个字段所有变量的值_matlab读取struct类型数据中的值-程序员宅基地

文章浏览阅读7.5k次,点赞5次,收藏19次。matlab结构体struct字段变量值提取_matlab读取struct类型数据中的值

Android fragment的用法_android reader fragment-程序员宅基地

文章浏览阅读4.8k次。1,什么情况下使用fragment通常用来作为一个activity的用户界面的一部分例如, 一个新闻应用可以在屏幕左侧使用一个fragment来展示一个文章的列表,然后在屏幕右侧使用另一个fragment来展示一篇文章 – 2个fragment并排显示在相同的一个activity中,并且每一个fragment拥有它自己的一套生命周期回调方法,并且处理它们自己的用户输_android reader fragment

FFT of waveIn audio signals-程序员宅基地

文章浏览阅读2.8k次。FFT of waveIn audio signalsBy Aqiruse An article on using the Fast Fourier Transform on audio signals. IntroductionThe Fast Fourier Transform (FFT) allows users to view the spectrum content of _fft of wavein audio signals

随便推点

Awesome Mac:收集的非常全面好用的Mac应用程序、软件以及工具_awesomemac-程序员宅基地

文章浏览阅读5.9k次。https://jaywcjlove.github.io/awesome-mac/ 这个仓库主要是收集非常好用的Mac应用程序、软件以及工具,主要面向开发者和设计师。有这个想法是因为我最近发了一篇较为火爆的涨粉儿微信公众号文章《工具武装的前端开发工程师》,于是建了这么一个仓库,持续更新作为补充,搜集更多好用的软件工具。请Star、Pull Request或者使劲搓它 issu_awesomemac

java前端技术---jquery基础详解_简介java中jquery技术-程序员宅基地

文章浏览阅读616次。一.jquery简介 jQuery是一个快速的,简洁的javaScript库,使用户能更方便地处理HTML documents、events、实现动画效果,并且方便地为网站提供AJAX交互 jQuery 的功能概括1、html 的元素选取2、html的元素操作3、html dom遍历和修改4、js特效和动画效果5、css操作6、html事件操作7、ajax_简介java中jquery技术

Ant Design Table换滚动条的样式_ant design ::-webkit-scrollbar-corner-程序员宅基地

文章浏览阅读1.6w次,点赞5次,收藏19次。我修改的是表格的固定列滚动而产生的滚动条引用Table的组件的css文件中加入下面的样式:.ant-table-body{ &amp;::-webkit-scrollbar { height: 5px; } &amp;::-webkit-scrollbar-thumb { border-radius: 5px; -webkit-box..._ant design ::-webkit-scrollbar-corner

javaWeb毕设分享 健身俱乐部会员管理系统【源码+论文】-程序员宅基地

文章浏览阅读269次。基于JSP的健身俱乐部会员管理系统项目分享:见文末!

论文开题报告怎么写?_开题报告研究难点-程序员宅基地

文章浏览阅读1.8k次,点赞2次,收藏15次。同学们,是不是又到了一年一度写开题报告的时候呀?是不是还在为不知道论文的开题报告怎么写而苦恼?Take it easy!我带着倾尽我所有开题报告写作经验总结出来的最强保姆级开题报告解说来啦,一定让你脱胎换骨,顺利拿下开题报告这个高塔,你确定还不赶快点赞收藏学起来吗?_开题报告研究难点

原生JS 与 VUE获取父级、子级、兄弟节点的方法 及一些DOM对象的获取_获取子节点的路径 vue-程序员宅基地

文章浏览阅读6k次,点赞4次,收藏17次。原生先获取对象var a = document.getElementById("dom");vue先添加ref <div class="" ref="divBox">获取对象let a = this.$refs.divBox获取父、子、兄弟节点方法var b = a.childNodes; 获取a的全部子节点 var c = a.parentNode; 获取a的父节点var d = a.nextSbiling; 获取a的下一个兄弟节点 var e = a.previ_获取子节点的路径 vue