”vivado生成ltx文件命令“ 的搜索结果

前言EDF文件可以直接导入Vivado,而无需Verilog源文件。...软件版本:Vivado2018.3流程生成EDF网表文件(1)设置需提交的源代码的最顶层为TOP层。可以看到内部调用了2个IP块。(2)在设置选项的综合设置中...

这里从两个方面分别进行说明,为什么要使用Vivado的Batch mode。1、流程操作效率我所谓的流程操作效率,是指在使用Vivado时,通过键盘输入、鼠标点击以及进行等待等实际外部操作的效率。例如我需要打开一个Vivado...

之前的文章介绍了FPGA在线调试的方法,包括选定抓取信号,防止信号被优化的方法等等。当存在多种参数的场景时,意味着我们需要多次综合布局布线,这十分浪费时间,虽然只是修改一个数值。而本文将介绍FPGA在线调试的...

Xilinx Artix-7系列FPGA 高速采集卡开发例程使用手册Xilinx Artix-7 系列FPGA 高速采集卡开发例程使用手册Revision HistoryDraft Date Revision No. Description2016/07/07 V1.3 1. 添加PCIE_SGDMA_ADC 采集显示例程...

本文介绍了针对VIVADO开发工具的在线分析工具的使用方法。例如,如何添加被测信号,如何准确的观测到被测信号的典型现象,以及通常会遇到的问题等。

工程比特流生成完必后,run tcl script,可在*.dbg路径下找到拷贝出来的2个文件。vivado默认generate bitstream的路径为impl文件夹中,需要点很多次路径去找,可使用下脚本代替人工操做,将文件复制到外层工程路径中...

Vivado Tcl Shell是一种内置在Vivado中的交互式解释器,它支持Tcl语言和Vivado Shell命令,用户可以通过Tcl脚本在Vivado Tcl Shell中执行各种命令,自动化地完成Vivado工程的创建、配置、仿真等操作。本文介绍了如何...

假设此时已经在Vivado上完成了逻辑的综合、实现,并生成了编程文件.bit。下一步要导出硬件说明文件到sdk,用于软件的开发。导出硬件说明文件到SDK图1. 选择 “File>>Export>>Export Hardwdare....”导出...

利用Vivado创建工程的方法,尽在掌握! 说在前面的话: 本人也是初学者,本文将以笔记的方式展现Vivado工具的操作方法,没有图片,因为我觉得这样更快一点上手。下面的内容包括工程的创建,带EMIO引脚配置以及不带...

1.在IP核中找到ILA2.General Options(常规选项)主要有如下三部分:1.Monitor Type:ILA 探针接口类型设置,ILA 探针接口有两种类型,Native 与 AXI。Native 是普通接口模式;AXI 是 AXI 接口模式,用于调试 AXI ...

Vivado工程在编译过程中产生很多临时文件,备份文件非常之大,经查阅有以下3种方法: 保存tcl脚本 工程复位 全部备份 保存tcl脚本方法 打开Vivado工程,点击Project-Write Project tcl,保存tcl到工程目录,并将...

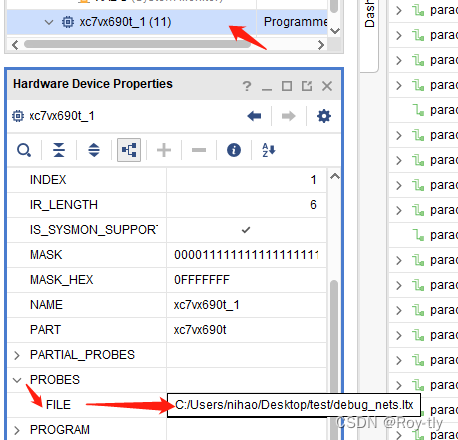

从Vivado软件的console窗口中拷贝UI操作产生的TCL命令,整理成一个TCL脚本,将里面特定的字串做成参数传递的形式传入,在TCL脚本内可用这种方式接收参数: set ltx_file [lindex $argv 0] puts "ltx_file = $ltx_...

There are three stages in vivado from RTL to Bitstream(从逻辑设计到bitstream的三个阶段) 综合: 这个步骤将会把你的硬件语言代码转换成netlist。In Synthesizeprocess, RTL design (verilog/VHDL) is ...

使用Vivado软件进行硬件调试

标签: zynq

vivado在线调试、在线抓波形方法

Vivado ML 2021.1 安装包下载 (Full Product Installation) 官网下载地址 网盘链接提供 以下为更新介绍 Vivado ML 新增功能(按类别划分) 展开以下部分,进一步了解 Vivado® ML 2021.1 的新功能和增强功能。 ...

vivado 使用 Tcl 命令来与 JTAG-to-AXI Master 核进行交互、使用 Tcl 命令来执行 ILA 测量

本文介绍一个Quartus工具支持但是ISE/Vivado不支持的小功能,并给出Vivado的实现方案,让Xilinx FPGA的开发/使用也更加便利。在使用FPGA做设计的时候,有时候的一些场景,不太适合仿真来进行验证。比如:1.已经完成...

使用脚本综合实现工程是十分便利的,下面介绍一种方便,快捷的方式实现vivado的non-project模式。开发者不用深入了解tcl语法,一样可以做到。

当然也包含debug core在里面ltx文件是在hardware manager里面如果去显示debug core所连接的带观测信号,比如信号名,位宽,是否是bus,顺序等等如果用SDK工具加载在HW manager里面看到的debug信号跟vivado下载看到的...

推荐文章

- withRouter,非根组件获取路由参数_withrouter 只能取到路由中的一个参数-程序员宅基地

- ubuntu环境下QT5操作摄像头报错,cannot find -lpulse-mainloop-glib cannot find -lpulse cannot find -lglib-2.0_cannot find–lpulse-程序员宅基地

- 用jbpm_bpel学jwsdp的ant方式使用-程序员宅基地

- 输入数字判断星期几_html获取当前星期几-程序员宅基地

- SpringBoot整合Activiti7——实战之放假流程(会签)_activit7中会签-程序员宅基地

- 阿里云服务器收到挖矿病毒的攻击,导致基础的文件被病毒污染的问题和对应的处理解决方法-程序员宅基地

- 北京东城区空调维修办法,格力变频空调出现ph,到底是怎么回事?_格力变频空调ph代码-程序员宅基地

- vscode编辑器使用拓展插件background添加背景图片改变外观_background vscode-程序员宅基地

- android 简单打电话程序_android拨打电话的程序-程序员宅基地

- 第二届中国(泰州)国际装备高层次人才创新创业大赛_泰州市双创人才计划2022-程序员宅基地