A、在原理图(block design)右击添加“Mark Debug”,工程综合后,在SYNTHESIS > Open Synthesized Design,在Netlist窗口中选择需要调试的网络节点,进行调试。根据实际的输出结果表现,来推测可能的原因,再在...

”fpga在线调试“ 的搜索结果

本文基于上文的工程文件,讲述了 fpga 内嵌逻辑分析仪的使用方法,内嵌逻辑分析仪是在 fpga 开发调试过程中一个很重要的一个工具,这个工具可以帮助我们去观察内部的一些信号它的一些变化,然后帮助我们去调试从而...

在设计基于FPGA的电子系统时,一般需要用示波器、逻辑分析仪等外部测试设备进行输入输出信号的测试,借助测试探头把信号送到测试设备上进行观察分析。当然,前提是需要保留足够多的引脚,以便能选择信号来驱动I/O...

本文介绍了针对VIVADO开发工具的在线分析工具的使用方法。例如,如何添加被测信号,如何准确的观测到被测信号的典型现象,以及通常会遇到的问题等。

Actel FPGA在线配置图文解说。

1.1 抓取需探测的信号 1.2 综合并建立 debug 1.3 实现并生产 bit 流文件 1.5 上板观察 1.6 注意事项

在设计基于FPGA的电子系统时,一般需要用示波器、逻辑分析仪等外部测试设备进行输入输出信号的测试,借助测试探头把信号送到测试设备上进行观察分析。当然,前提是需要保留足够多的引脚,以便能选择信号来驱动I/O...

基于In-system memory content editor的FPGA在线调试方法.pdf

高云FPGA调试记录(一)点灯

1.LED的妙用。2.当存在调用大分频元件时的仿真。3.串口的作用。

FPGA与PC串口调试工具通信程序,包括收和发两个过程。

一种基于网络的FPGA远程调试加载方法.pdf

输出的频率不是精确的,比如驱动时钟是204.8MHz需要产生1MHz的正弦波形时如果相位的精度是32位,则每个时钟的相位增量就是(1M/204.8M)*(2^32) = 20,971,520 是一个整数,dds产生的正弦波频率为1MHz。...

之前的文章介绍了FPGA在线调试的方法,包括选定抓取信号,防止信号被优化的方法等等。当存在多种参数的场景时,意味着我们需要多次综合布局布线,这十分浪费时间,虽然只是修改一个数值。而本文将介绍FPGA在线调试的...

基于FPGA的串口调试,亲测无错误,用串口调试工具可直接实现!

在调试FPGA电路时要遵循一定的原则和技巧,才能减少调试时间,避免误操作损坏电路。一般情况下,可以参考以下步骤进行FPGA硬件系统的调试。 (1)首先在焊接硬件电路时,只焊接电源部分。使用万用表进行测试,...

利用京微fpgaH1芯片,测试fpga上mipi接口,rx——tx,速度1.5g,支持rgb进lvds进等

FPGA代码调试故障,辛苦积累,值得下载。强烈推荐。

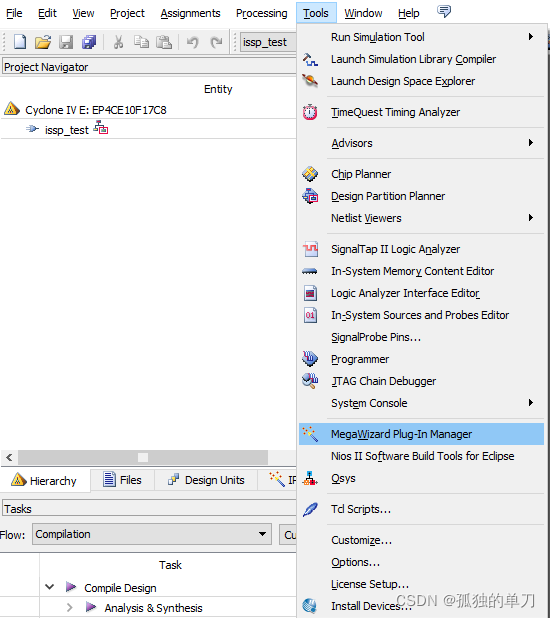

Altera公司的 QuartusII 支持的五种挺实用的调试方法: SignalProbe:信号探针方式不影响原有的设计功能和布局布线,只是通过增加额外布线将需要观察调试的信号连接到预先保留或者暂时不使用的 I/O 接口。该方式相应...

虽然不懂为什么但是今年fa

谈谈FPGA的在线调试工具.docx

V1.0加一起就3条指令,可以将XVC服务器运行在PC机上,QT直接运行即可,同时QT上位机完成XVC协议栈的数据payload的分发即可,分发协议为了平台移植性强,可以换成UDP协议,将数据分发给一个普通的FPGA,比如A7,A7上...

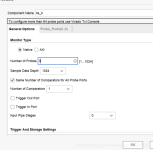

硬件调试是FPGA开发中非常重要的一环,能够占据开发周期的40%。本文主要是利用ISE的Chipscope插件进行硬件调试,侧重基本功能。 目录ISE软件硬件调试内置逻辑分析仪代码优化core inserter在线调试下载bit流文件到...

fpga verilog IIC 已经调试通过

在FPGA平台上运行,经过调试,是好使的,此程序能帮助使用者充分理解SDRAM的意义。

一种基于XVC协议的FPGA调试模块设计.pdf

推荐文章

- C++零碎知识点(一)-程序员宅基地

- 【Python学习笔记】Coursera课程《Python Data Structures》 密歇根大学 Charles Severance——Week5 Dictionary课堂笔记...-程序员宅基地

- v-html 解析字符串到 html 换行显示_html字符串 v-html-程序员宅基地

- 招收跨专业考计算机的学校,跨专业考研,接受跨专业考研的学校。-程序员宅基地

- 数学模型预测模型_改进著名的nfl预测模型-程序员宅基地

- ELK-FileBeat入门_filebeat 6.5.4 - windows-程序员宅基地

- 微信小程序架构图与开发_微信小程序框架图-程序员宅基地

- Node.js 下载与安装教程_node下载-程序员宅基地

- MySQL报错:The server time zone value '�й���ʱ��' is unrecognized or represents more than one time zone_连接失败! the server time zone value ' й ' is-程序员宅基地

- 数学与生活——读书笔记-程序员宅基地