2022东北大学软件学院计算机组成原理实验报告(七段数码管+乘法器+单周期CPU)_东北大学计算机组成原理实验报告七段数码管-程序员宅基地

东北大学软件学院计算机组成原理实验报告:总共有3个实验:1.七段数码管 2.乘法器 3.单周期CPU 。这门课最终得分94。

一.实验目的

1. 组合逻辑设计实验目的:

(1). 学习Logisim数字逻辑电路设计和模拟仿真平台的使用;

(2). 掌握组合逻辑电路的设计方法;

(3). 掌握带有无关项的数字逻辑电路化简方法;

(4). 掌握七段数码管的工作原理;

(5). 设计七段数码管译码电路,并且进行仿真测试。

2. 时序逻辑设计实验目的:

(1). 掌握使用FSM进行时序逻辑电路设计的总体流程;

(2). 理解Moore型有限状态机和Mealy型有限状态机的不同;

(3). 理解并掌握两种状态编码方式(二进制编码和独热编码);

3.单周期CPU设计实验目的:

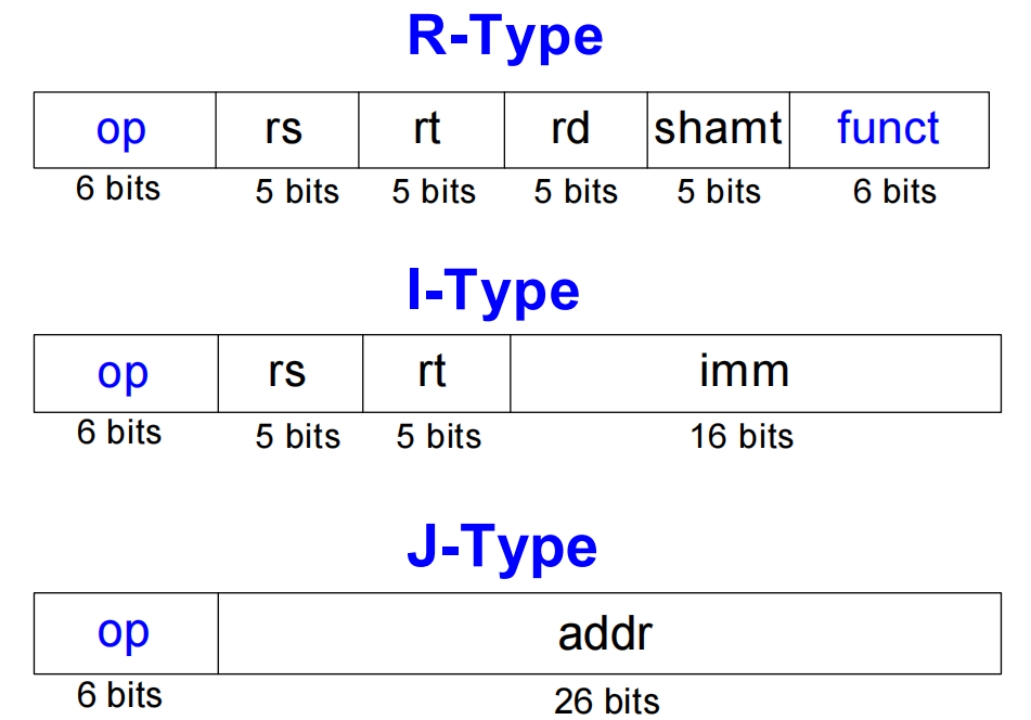

(1). 掌握MIPS体系结构,指令系统;

(2). 掌握MIPS机器指令三种类型指令的结构;

(3). 理解并掌握三种类型指令的执行过程;

(4). 掌握MIPS存储组件(寄存器,ROM,RAM)的工作原理;

(5). 掌握单周期MIPS CPU设计原理。

二.实验内容

1.1 七段数码管译码电路的设计需求

(1). 正确理解和区分逻辑函数中的无关项、约束项和任意项这三个基本概念,合理地运用无关项进行逻辑化简;

(2). 使用模拟逻辑电路的图形化工具Logisim;

(3). 设计的译码电路是一个独立的子电路,并进行封装及外观设计。

1.2 设计的目标内容

(1). 设计可正常显示0-9的实验电路;

(2). 设计可正常显示0-9,大于9显示字母“E”的实验电路;

(3). 设计可正常显示0-F的实验电路;

(4). 设计可正常显示0-F(数字和字母)并有极性控制的实验电路;

(5). 设计七段数码管译码电路的测试电路,该测试电路可使用拨码开关作为测试输入源,七段数码管模块作为测试输出。

2.时序逻辑设计

2.1 时序逻辑设计的设计需求

(1). 了解掌握有限状态机的基本原理,能够选择Moore型或Mealy型有限状态机设计乘法器;

(2). 深入了解乘法器设计的原理;

(3). 输入和输出的结果能够以十进制显示,并且能够正确显示结果;

2.2 设计的目标内容

(1). 可设计8位*8位,结果16位的基本乘法电路和控制器并能够正确计算和显示结果,电路设计美观,封装合理;

(2). 设计快速乘法器;

(3). 对基本乘法器和快速乘法器测试电路。

3.单周期CPU设计

3.1 单周期CPU的设计需求

(1). 设计一个MIPS体系结构的CPU,该CPU能够执行R类型、lw、sw、beq和bne类型的指令;

(2). 该CPU能够实现测试的用例,并且输出正确结果。

3.2 设计的目标内容

(1). 设计构建CPU所必要的组件,包括ALU、ROM、RAM,寄存器文件,电路设计美观,封装合理;

(2). 设计并实现MIPS单周期CPU数据通路和控制器,能够设计测试用例进行有效测试。

三.实验环境

-

七段数码管译码电路实验中使用的logisim库有:线路、逻辑门、存储库和输入输出。

-

乘法器设计的实验中使用的logisim库有:线路、逻辑门、存储库、复用器、运算器和输入输出。

-

单周期CPU实验中使用的logisim库有:线路、逻辑门、存储库、复用器、运算器和输入输出。

四.实验过程

1.组合逻辑设计

1.1 七段数码管译码电路的设计思路

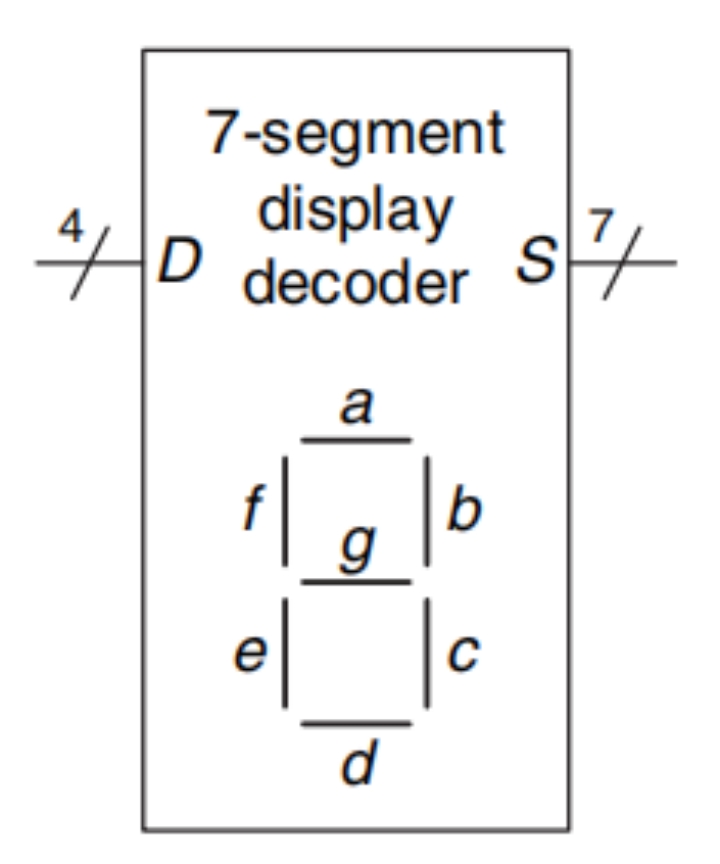

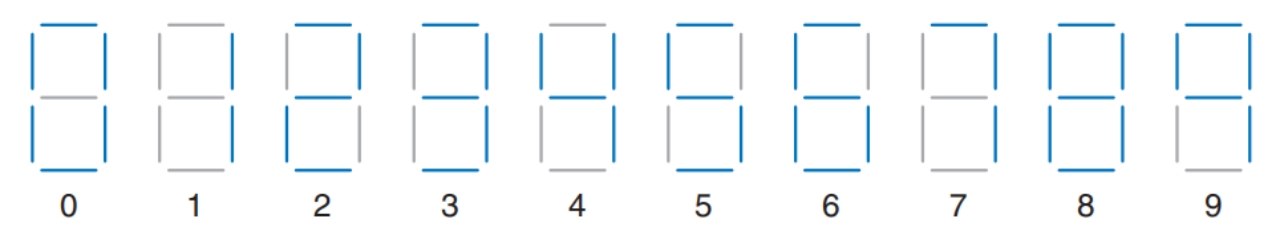

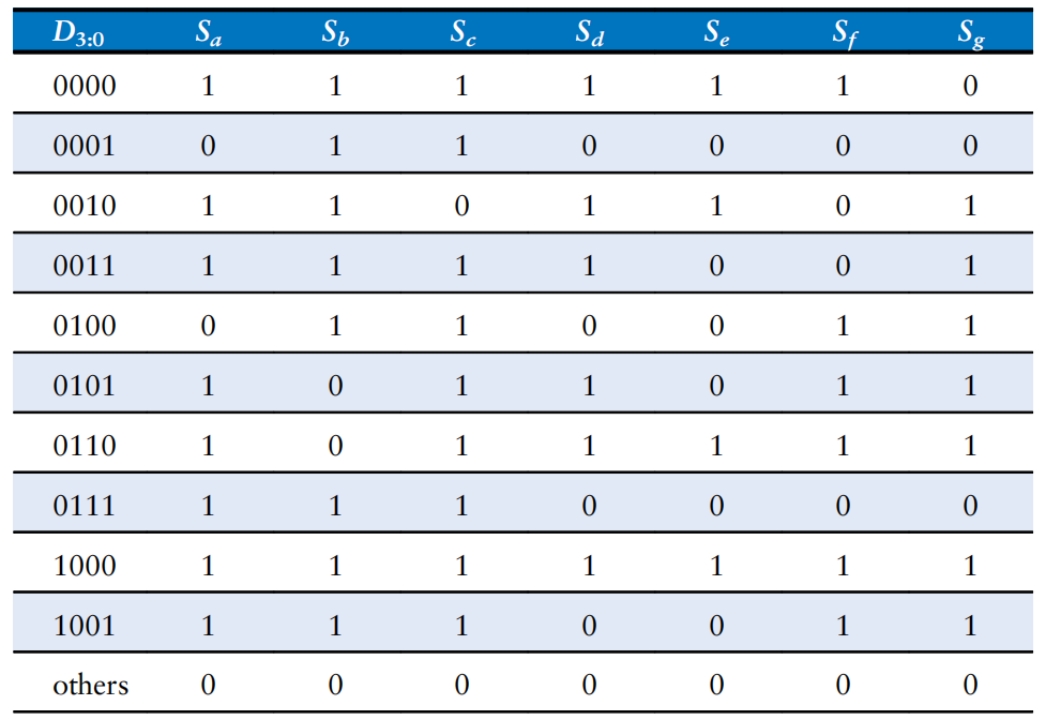

七段数码管显示译码器通过4位数据的输入,产生7位输出以控制发光二极管来显示数字0到9,这7位输出我们称为段a到段g。

图 1 七段数码管显示译码器电路符号

图 2 七段数码管显示的数字

图 3 七段数码管显示译码器真值表

1.2 设计方案

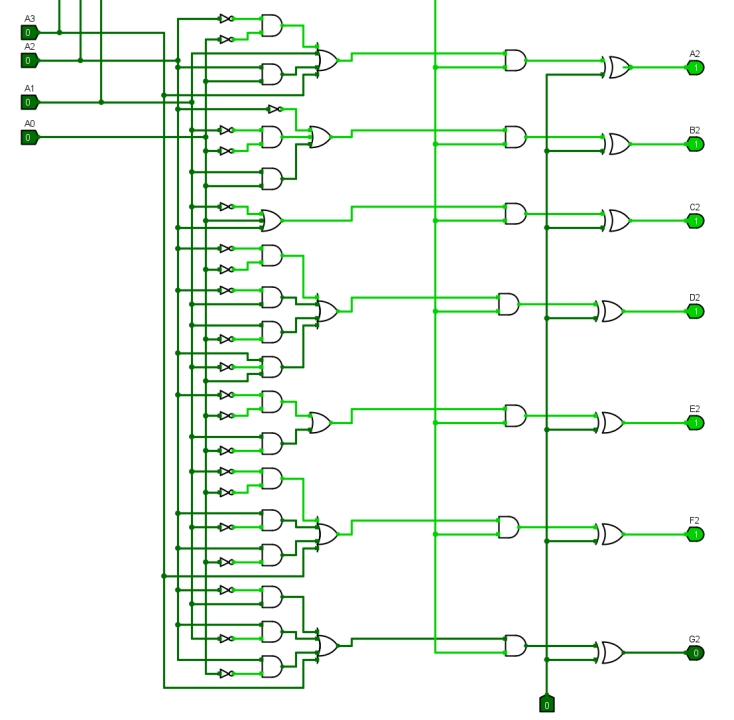

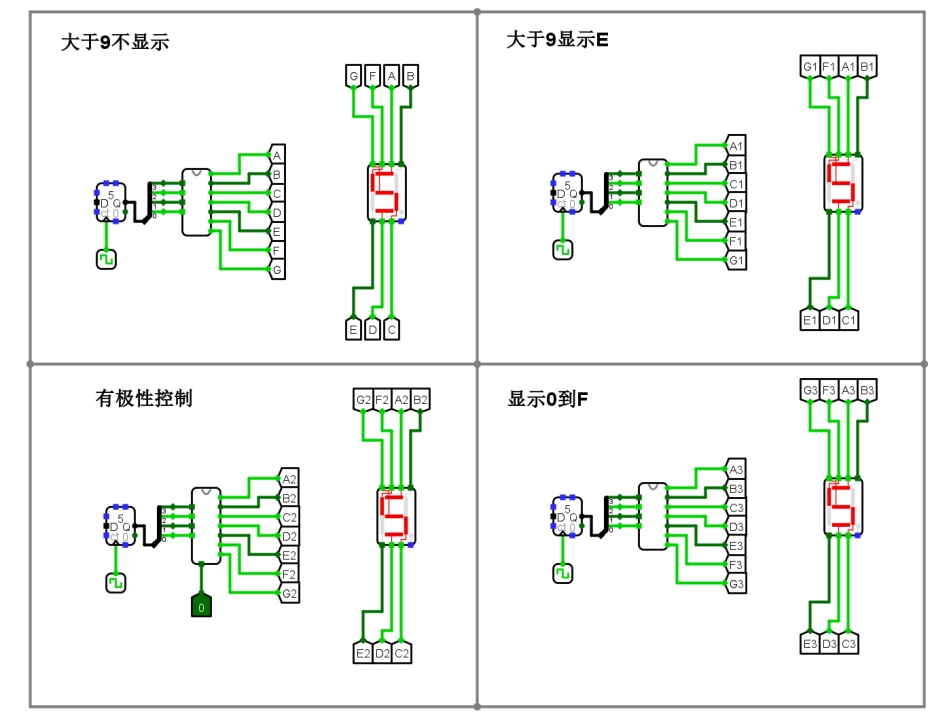

我总共设计了四种类型的方案,分别是只显示0到9且大于9不显示的电路、显示0到9且大于9显示E的电路、显示0到F的电路和显示0到F且有极性控制的电路。在这四种方案中,我认为显示0到F且有极性控制的电路最具有创新性。有极性控制能够扩大七段数码管的通用性,做到能共阳极或共阴极。

1.3 创新点

创新点是实现显示0到F且有极性控制的译码器。为了能够实现10到15显示字母,在原来的基础上,我多加考虑了1010到1111的真值表。为了实现极性的控制,在原来的输出结果加上了异或门逻辑。

图 4 七段数码管有极性控制的电路

2.时序逻辑设计

2.1 乘法器的设计思路

(1). 乘法器的原理

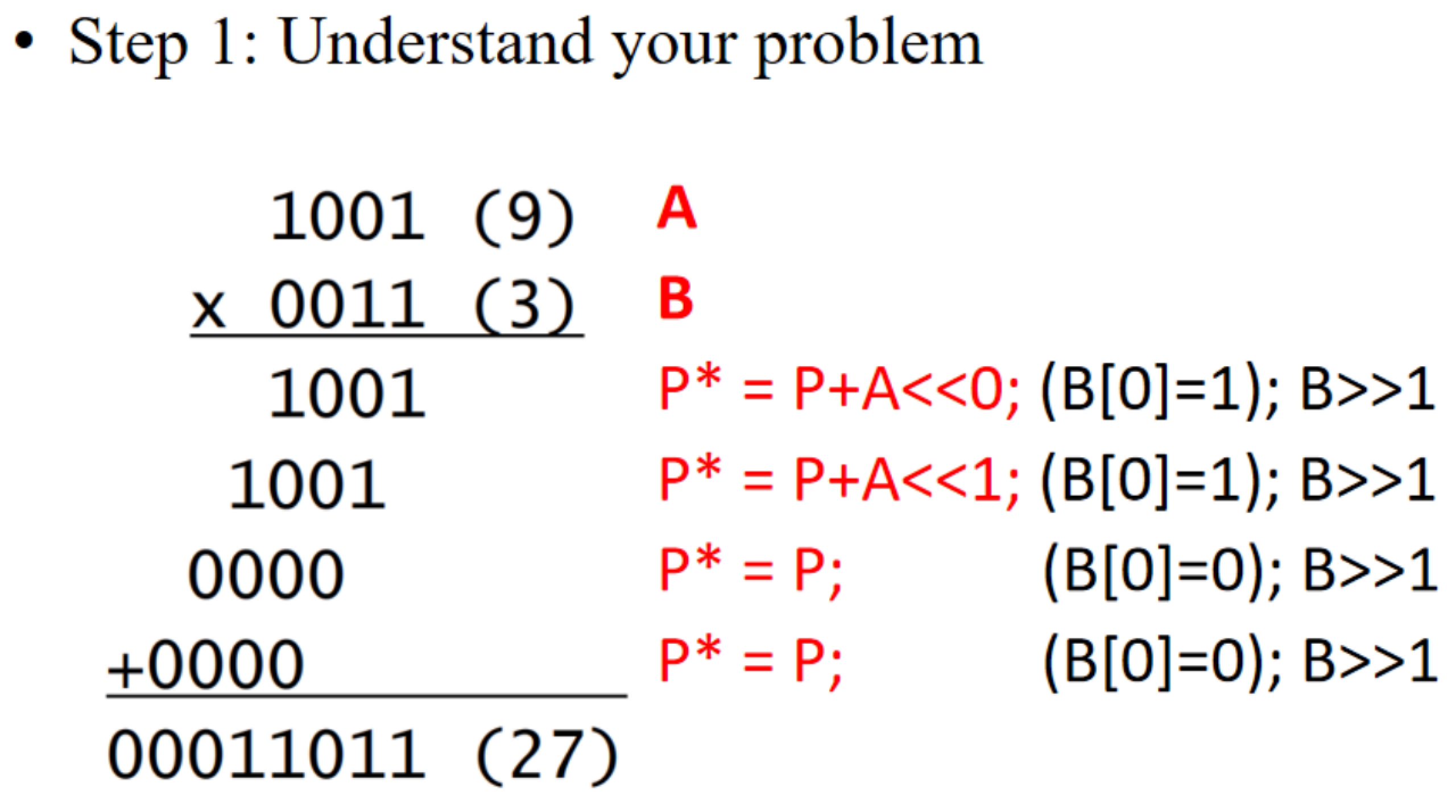

在设计乘法器之前,我们要理解乘法器的原理。在做乘法运算时,分为乘数和被乘数。我们记被乘数为A,乘数为B。乘法的计算过程如下图所示:

图 5 乘法的计算过程

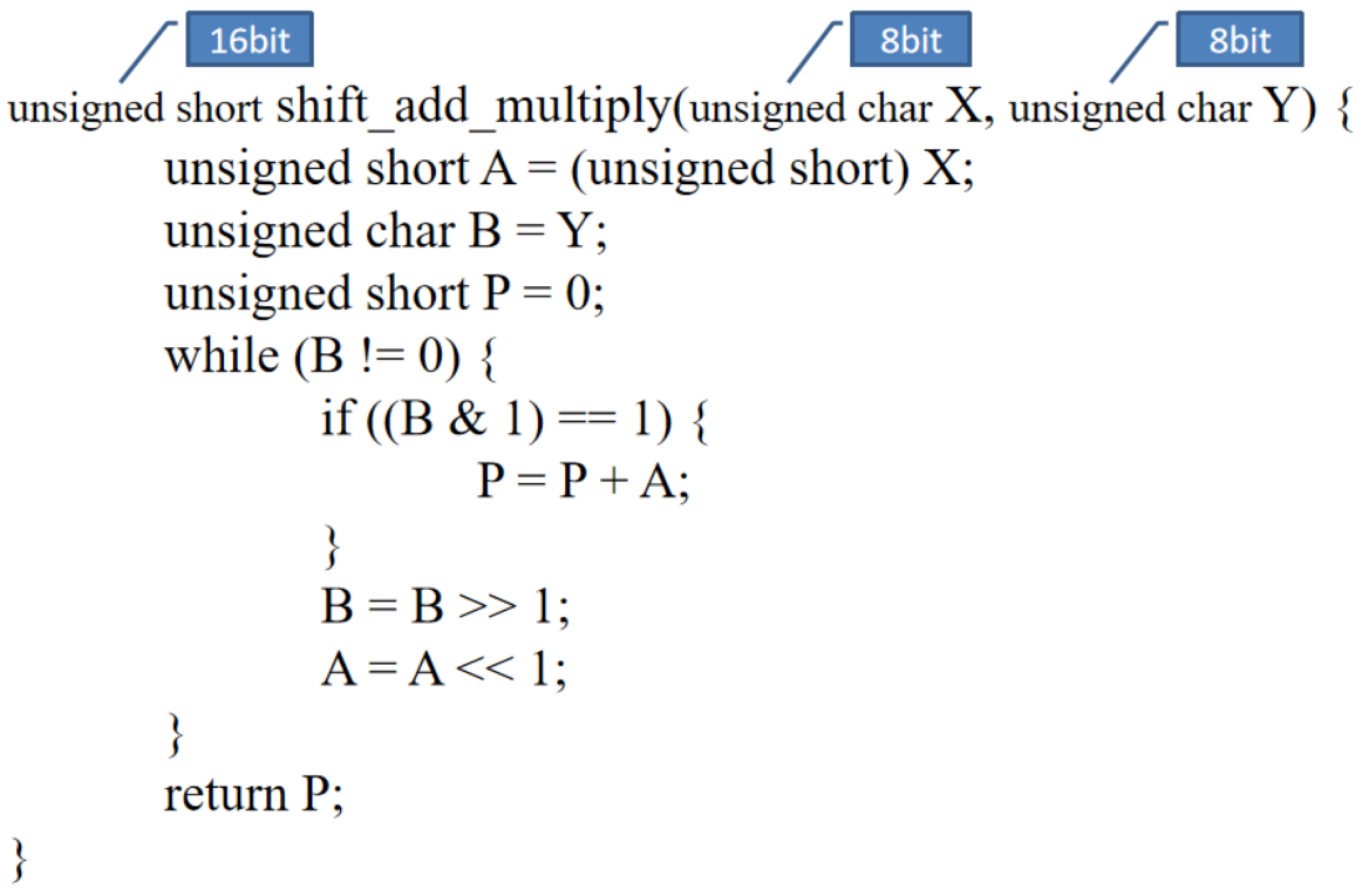

我们记乘数的每一位相乘后得到的结果为P,在乘法运算中,需要判断乘数是否为0,若乘数不是0,则进一步判断乘数的最低位是否为0,如果最低位是0,则P还是原来的结果,如果最低位是1,则P等于P加上A左移一位后的结果。我们可以用C语言代码的形式表示出乘法运算的整个流程。

图 6 乘法器C语言代码

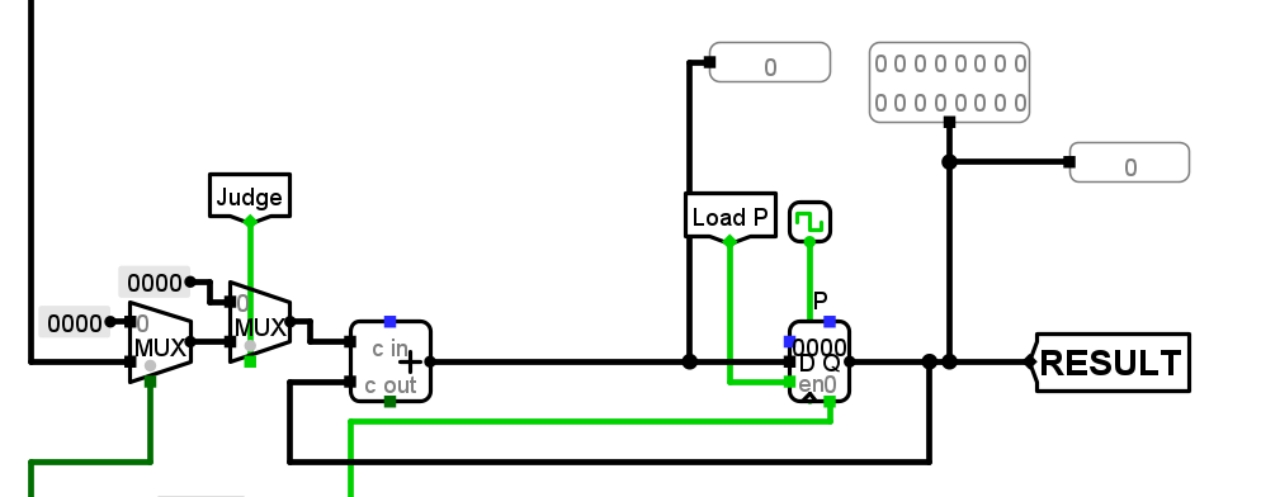

(2). 修改变量的状态

对于变量的修改,我们需要在电路图中实现。对于“P*=P+A”,我们在开始的时候给P赋值为0, 当进行第一步运算时,且最低位为1,那么P*的值就等于0加A,其实就是等于A。我使用了多路选择器,其中的Jugdge信号是根据判断乘数Y的最低位是否为0得到的,Load P也是根据判断乘数Y的最低位是否为0得到的。我分析得到,当乘数的最低位是0时,Load P和judge都为0;当乘数的最低位是1时,Load P和judge为1。

| B[0] | jugdge | Load P |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 1 | 1 |

表 1 judge和Load P的真值表

图 7 实现P*=P+A

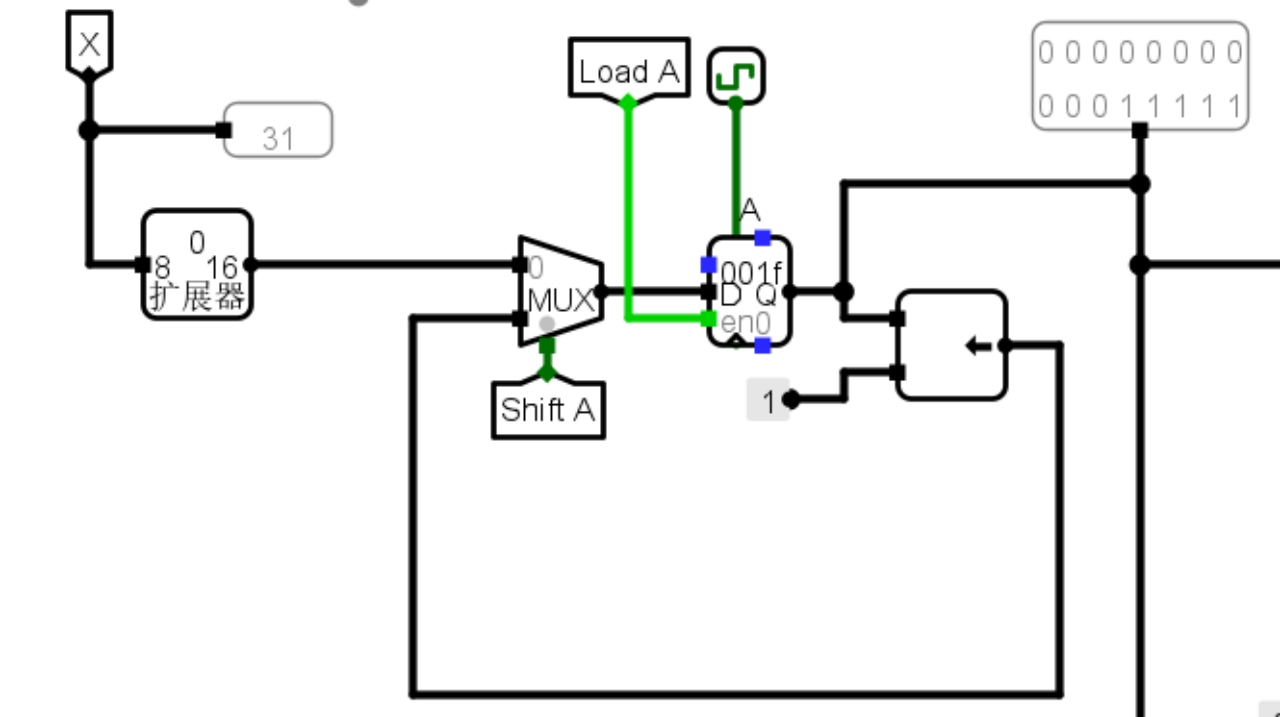

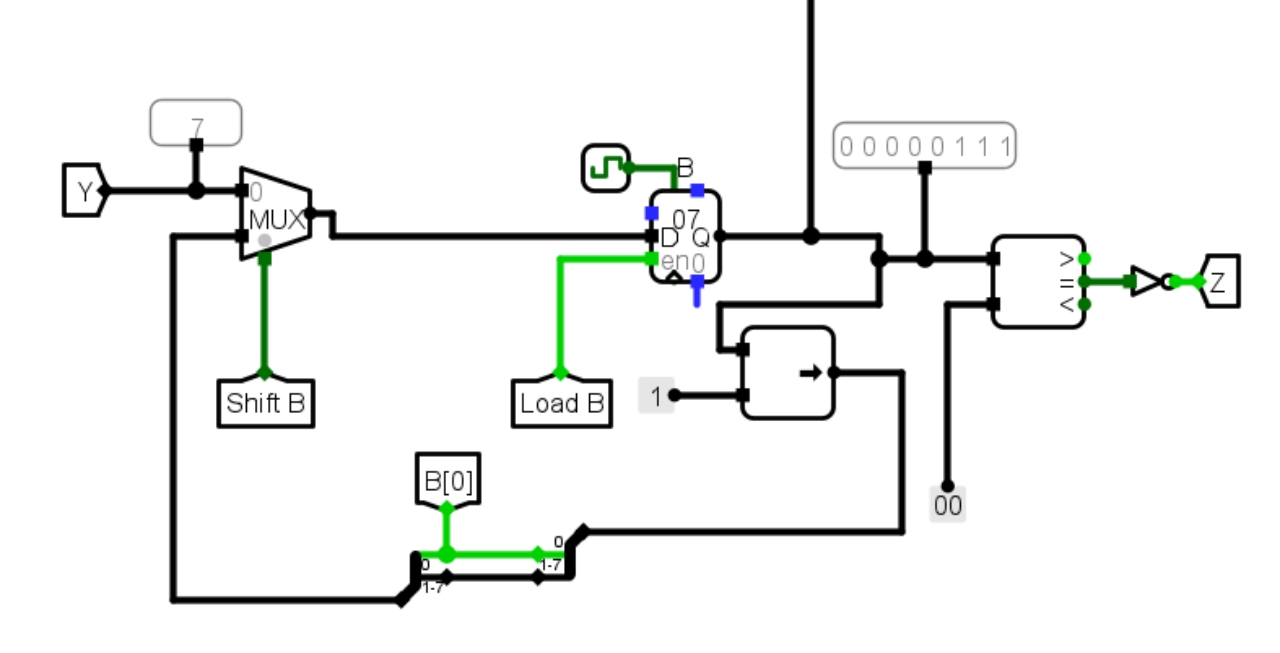

对于“B = B >> 1”和“A = A << 1”,我使用的是移位器来实现。在电路实现中我增加了Shift A和Shift B这两个信号,用来控制多路选择器,在最开始时,选择的是第0路,之后才会选择第1路,也就是移位后的A和B。

图 8 实现A = A << 1

图 9 实现B = B >> 1

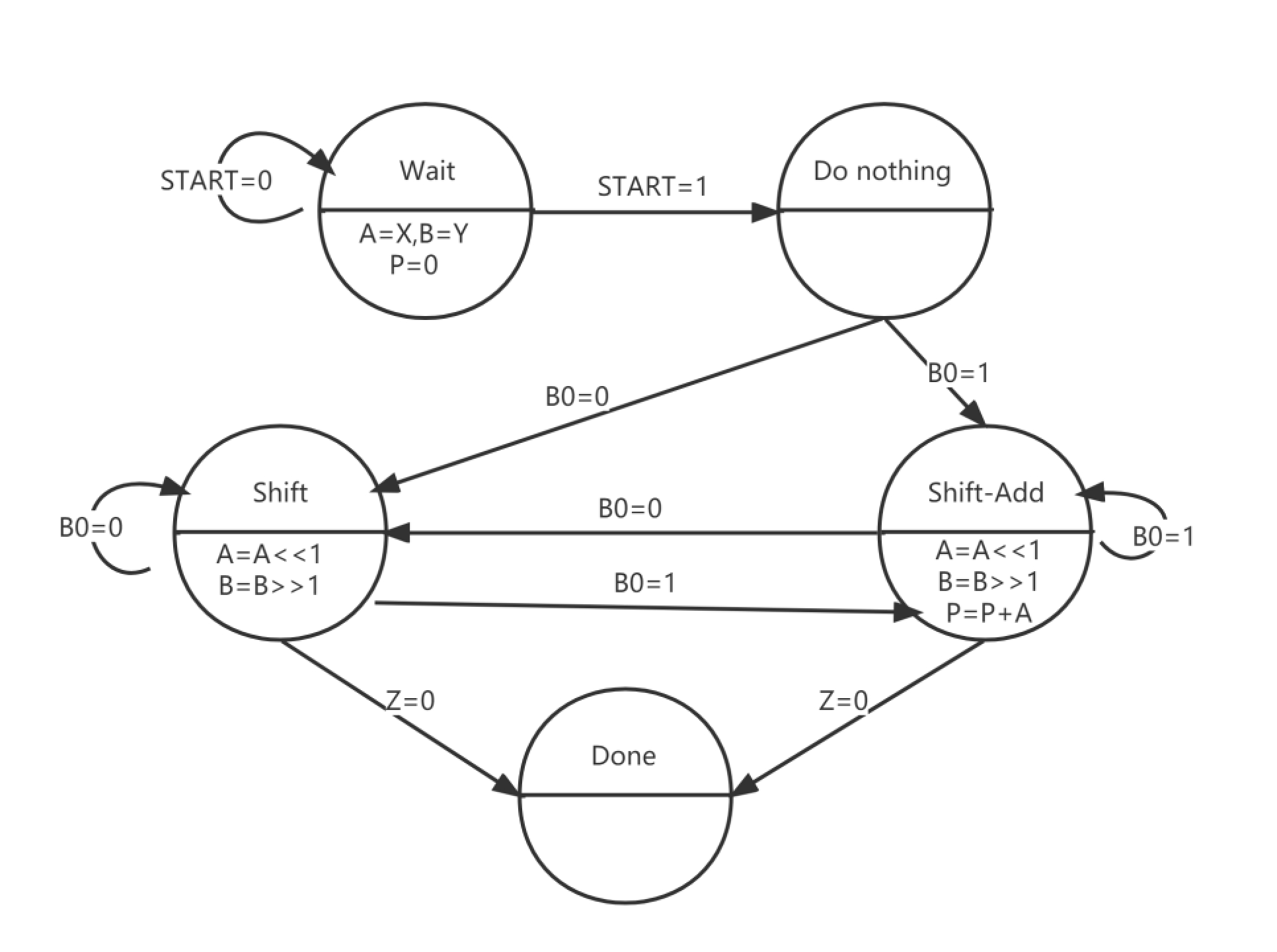

(3). 使用有限状态机实现乘法器的控制器

我设计的有限状态机中总共有5个状态,采用二进制编码的状态编码方式,我给这些状态分别记为000、001、010、011和100。

| 状态名称 | 二进制编码 | ||

|---|---|---|---|

| S2 | S1 | S0 | |

| Wait | 0 | 0 | 0 |

| Do nothing | 0 | 0 | 1 |

| Shift | 0 | 1 | 0 |

| Shift-Add | 0 | 1 | 1 |

| Done | 1 | 0 | 0 |

表 2 五种状态的二进制编码

可选择的状态机类型有Moore型和Mealy型,我使用的是Moore型的状态机,输出只取决于系统的状态。

| 当前状态****S2 S1 S0 | LA | SA | LB | SB | LP |

|---|---|---|---|---|---|

| 000 | 1 | 0 | 1 | 0 | 1 |

| 001 | 0 | 0 | 0 | 0 | 0 |

| 010 | 1 | 1 | 1 | 1 | 0 |

| 011 | 1 | 1 | 1 | 1 | 1 |

| 100 | 0 | 0 | 0 | 0 | 0 |

表 3 Moore型有限状态机输出表

| 当前状态S2 S1 S0 | 输入START | 输入B0 | 输入Z | 下一状态S2 S1 S`0 |

|---|---|---|---|---|

| 000 | 1 | 001 | ||

| 001 | 1 | 0 | 1 | 010 |

| 001 | 1 | 1 | 1 | 011 |

| 010 | 1 | 0 | 1 | 010 |

| 010 | 1 | 1 | 1 | 011 |

| 010 | 1 | 0 | 0 | 100 |

| 011 | 1 | 0 | 1 | 010 |

| 011 | 1 | 1 | 1 | 011 |

| 011 | 1 | 0 | 0 | 100 |

表 4 状态转移表

图 10 状态转换图

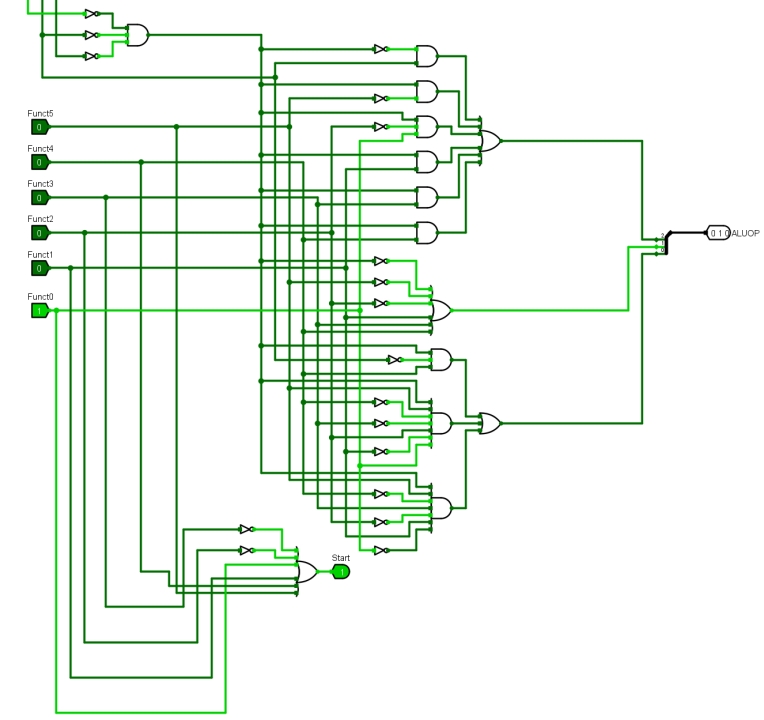

图 11 有限状态机电路图

2.2 设计方案

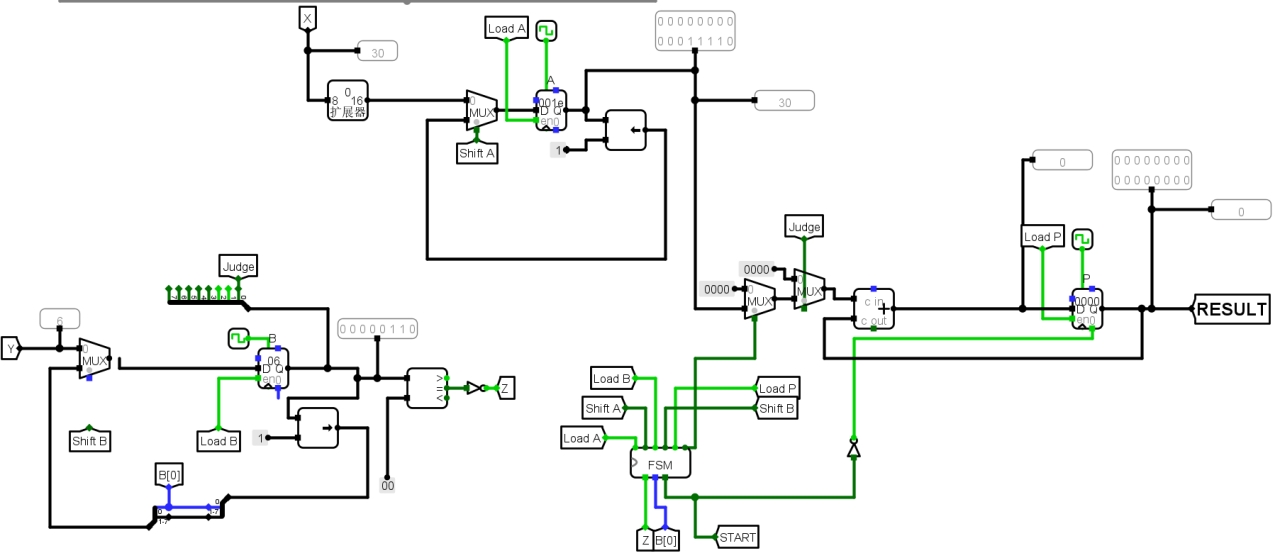

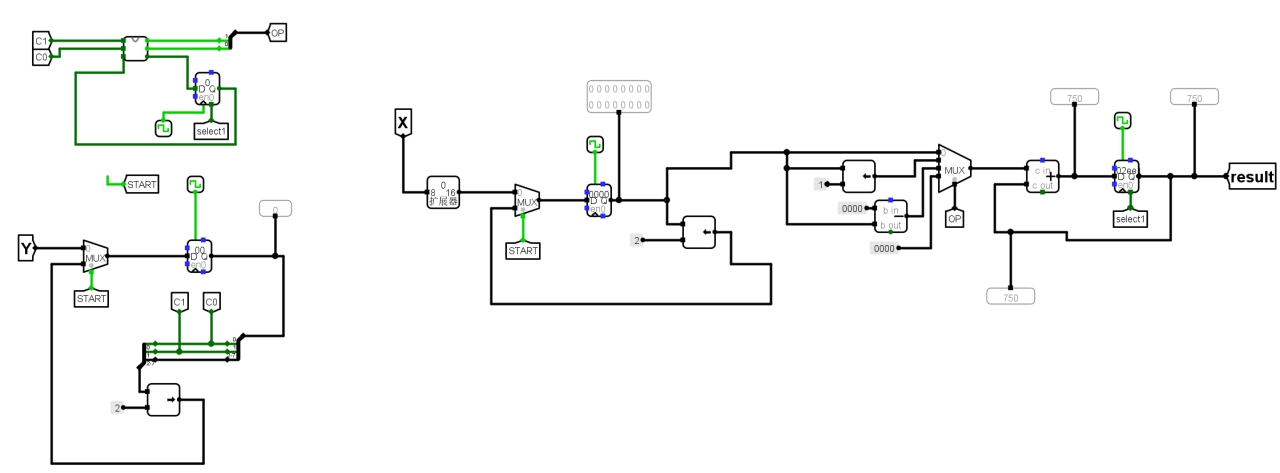

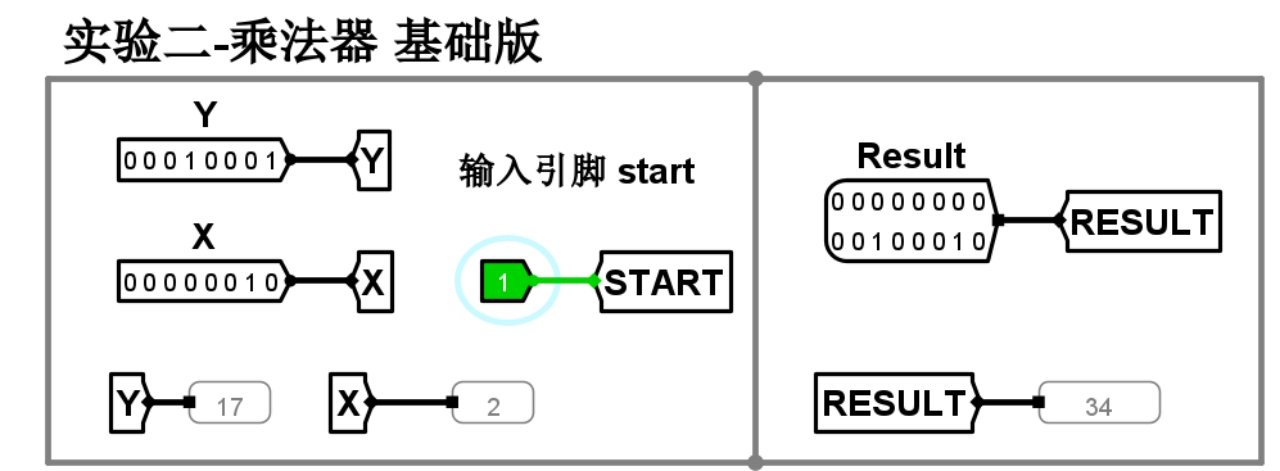

总共有两种设计方案,分别设计了的8位*8位,结果16位的基本乘法电路和moore型的控制器和快速乘法器。

图 12 基本乘法电路

2.3 创新点

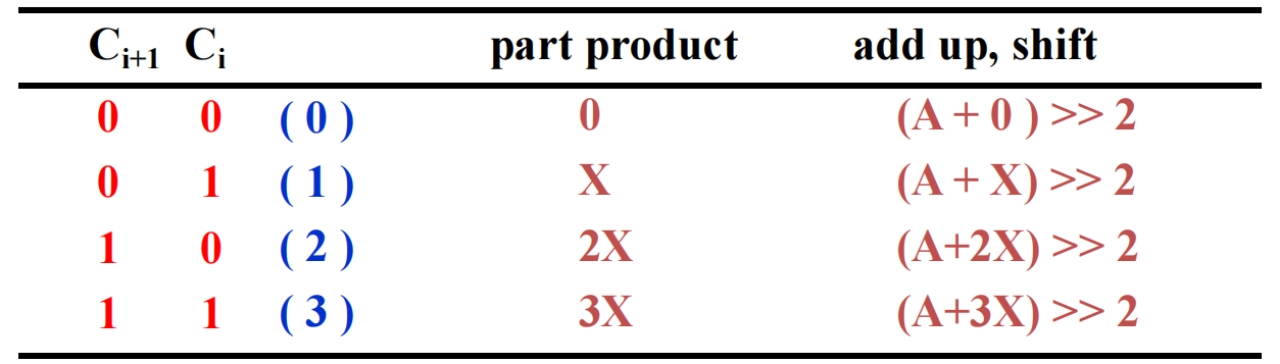

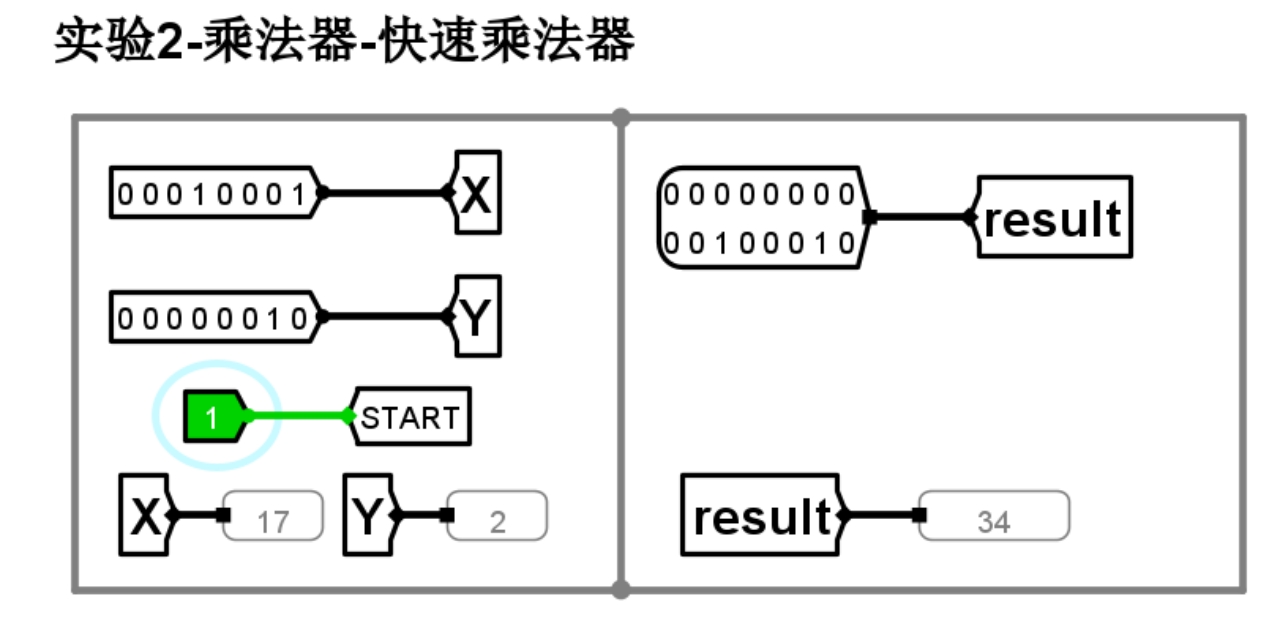

设计了快速乘法器,与基础版的乘法器不同的是,快速乘法器每一次运算的是两位(第0位和第1位),从而达到快速乘法的目的,提高计算的效率。

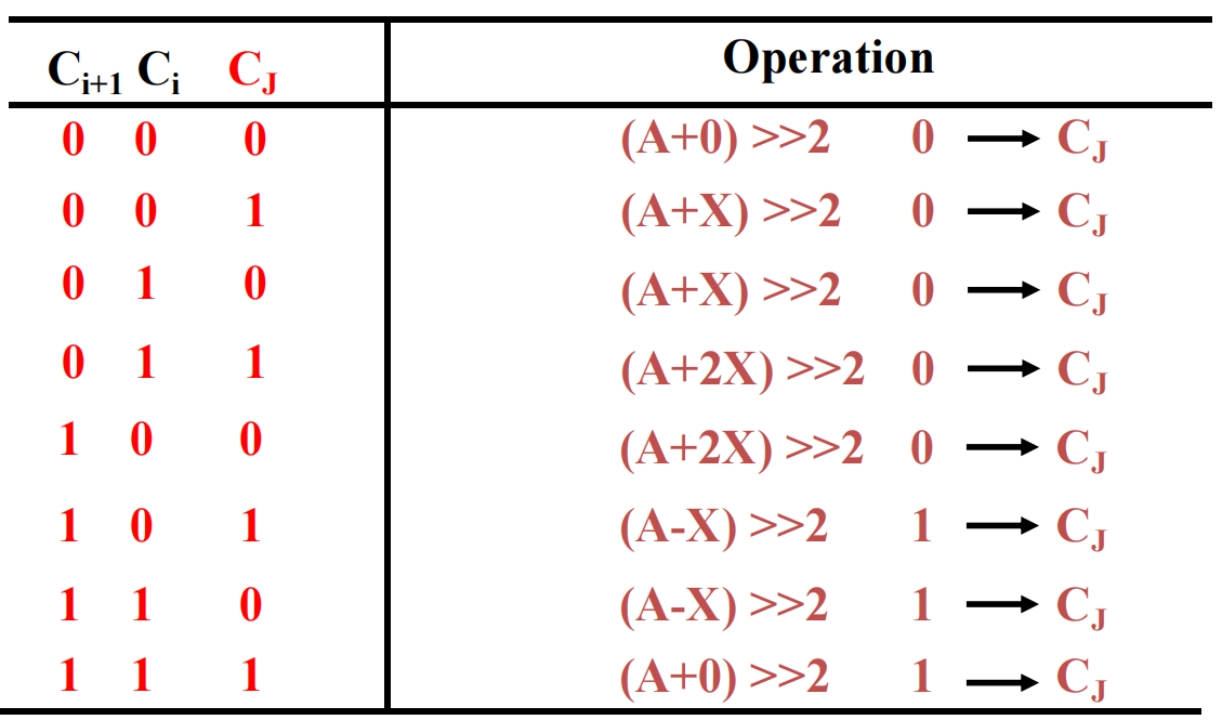

其中的A+3X是当成(A-X)+4X,这就需要引入CJ,CJ用来标记是否欠账,如果欠账了,则需要在下一步进行+X操作。

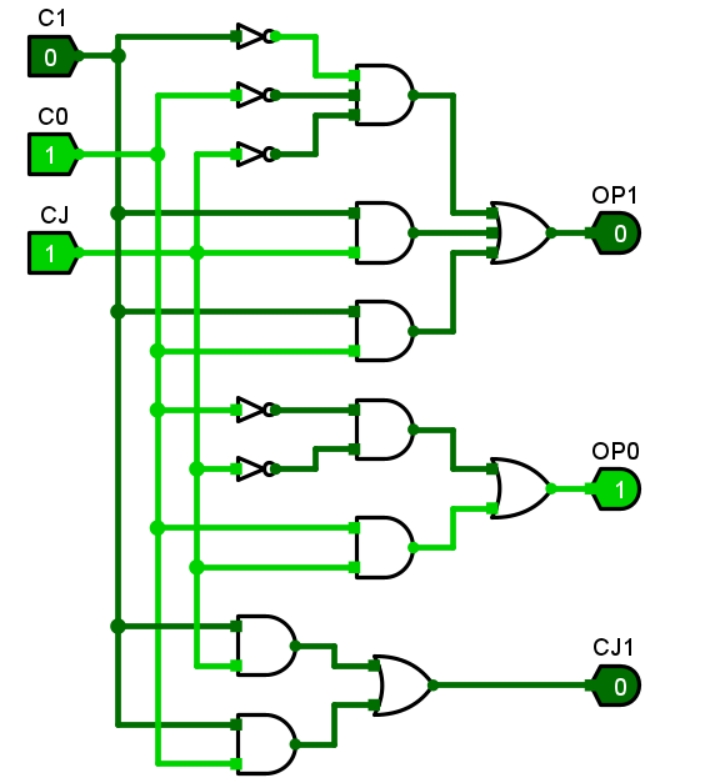

对于4中操作,我把它们看成是4种状态,用二进制编码表示出这4种状态。

| 操作 | OP1 | OP0 |

|---|---|---|

| **(A+**X) >>2 | 0 | 0 |

| (A+2X) >>2 | 0 | 1 |

| (A-X) >>2 | 1 | 0 |

| (A+0) >>2 | 1 | 1 |

图 13 四种状态的二进制编码

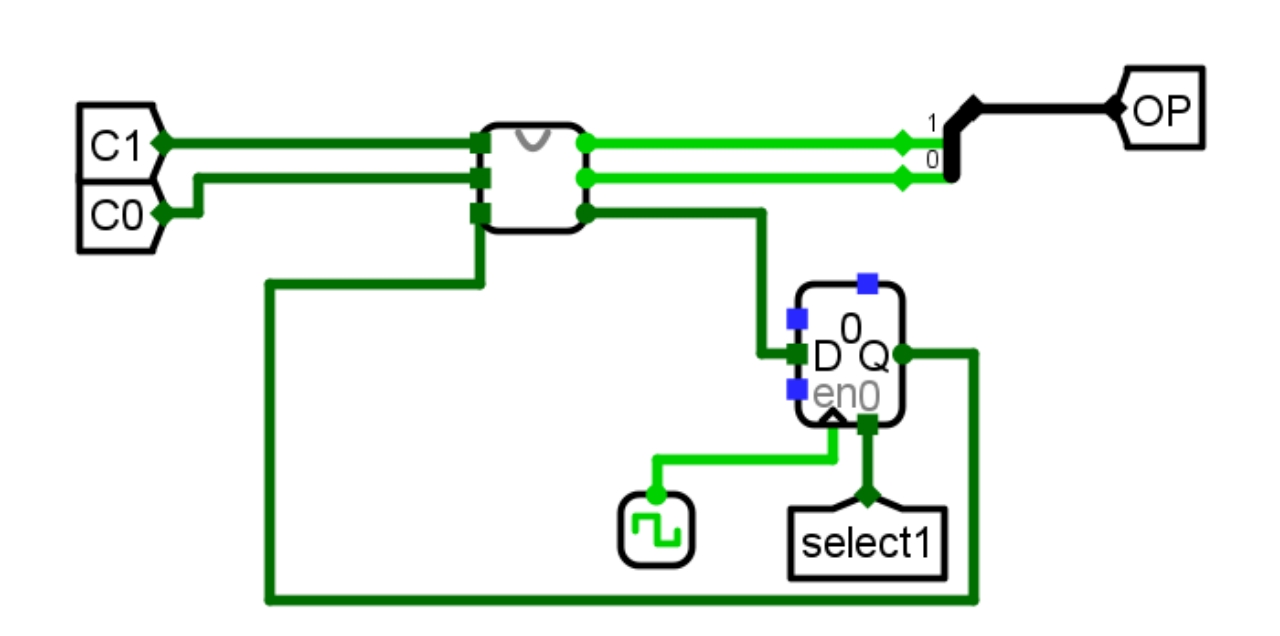

针对CJ,共有两种可能的情况,并且CJ的值与当前的最低两位相关,为此我设计了有限状态机。

图 14 有限状态机状态转移表

图 15 有限状态机电路图1

图 16 有限状态机电路图2

图 17 快速乘法器电路图

3.单周期CPU设计

3.1 设计所需组件

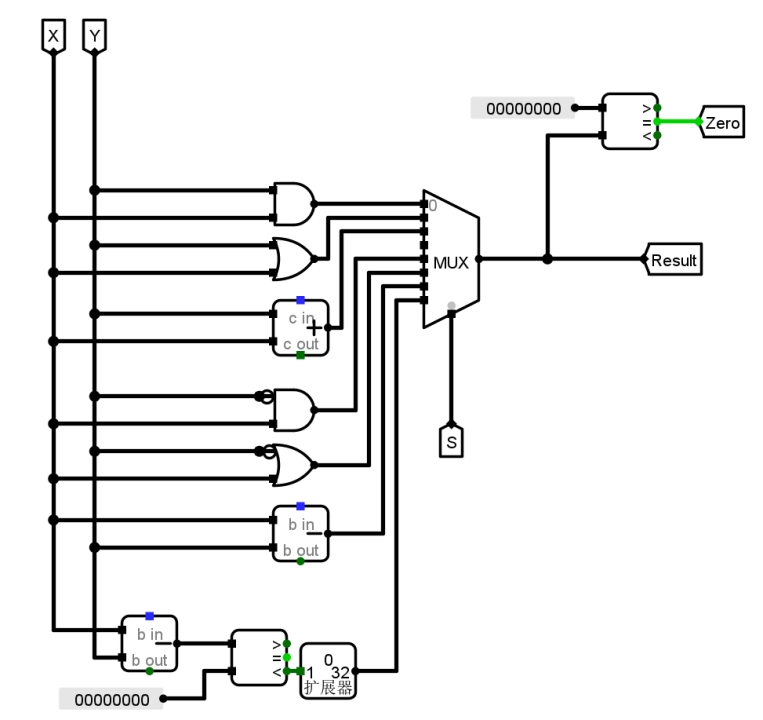

(1). ALU的设计

设计的ALU共有6种功能,并且有Zero信号用来表示最终的结果是否为0。设计的思想是3位的ALUOP作为多路选择器的选择信号,从而控制哪一路输出。

| ALUOP | 功能 |

|---|---|

| 000 | X AND Y |

| 001 | X OR Y |

| 010 | X + Y |

| 011 | 未使用 |

| 100 | X AND Y’ |

| 101 | X OR Y’ |

| 110 | X - Y |

| 111 | SLT |

图 18 ALU的功能

图 19 ALU设计电路

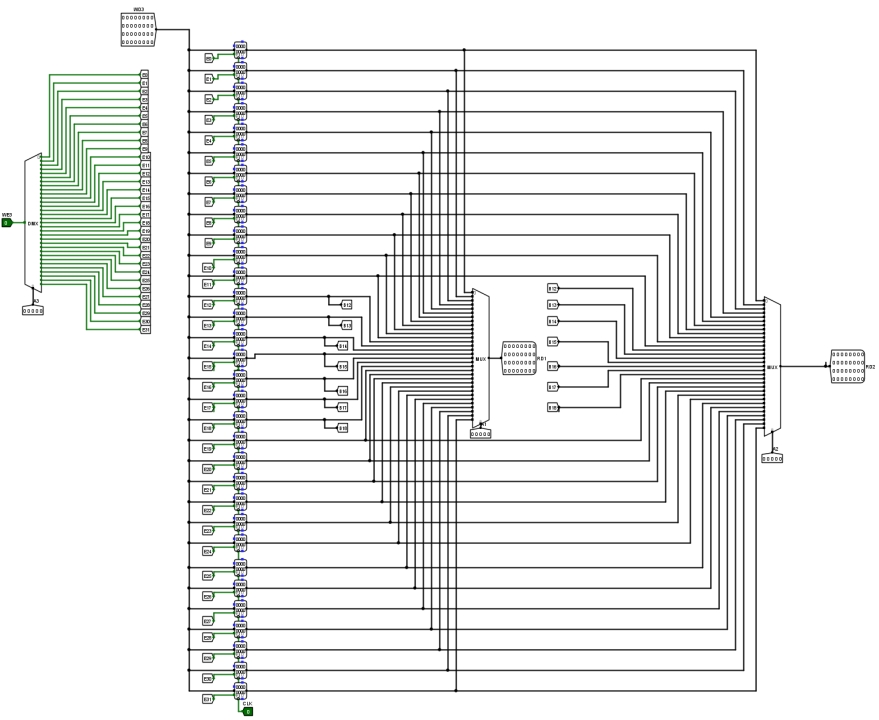

(2).寄存器文件的设计

设计了有一个写地址端口、一个写数据端口、一个写使能端口、两个读数据端口、两个读地址端口的寄存器文件,其中的数据端口的数据位宽是32位,地址端口的数据位宽是5位,设计的思想是把32个寄存器并行,通过多路选择器对输出的数据的寄存器选择,通过解复用器对需要写入的的寄存器选择。

图 20 寄存器文件设计电路

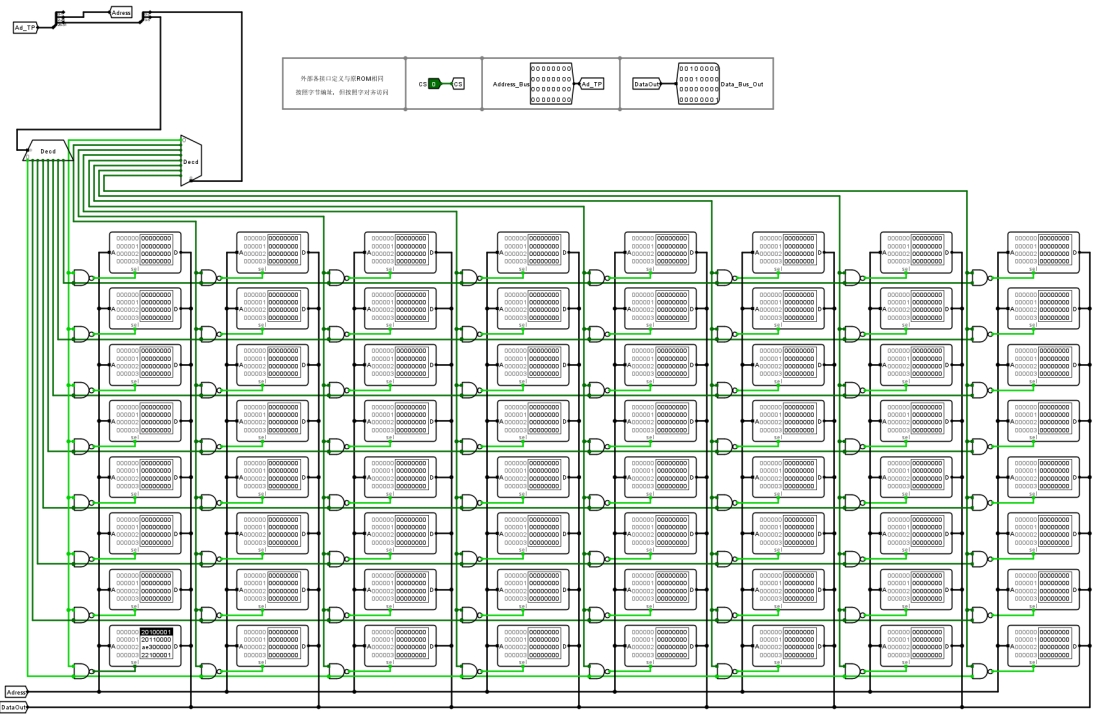

(3).Rom存储阵列的设计

Rom存储器是用来当指令存储器,程序计数器(PC)中包含当前执行指令的地址,第一步则需要从指令存储器中读取指令。我设计的Rom存储阵列由64个Rom组成,指令地址的最高6位构成存储阵列的片选逻辑。

图 21 Rom存储阵列电路

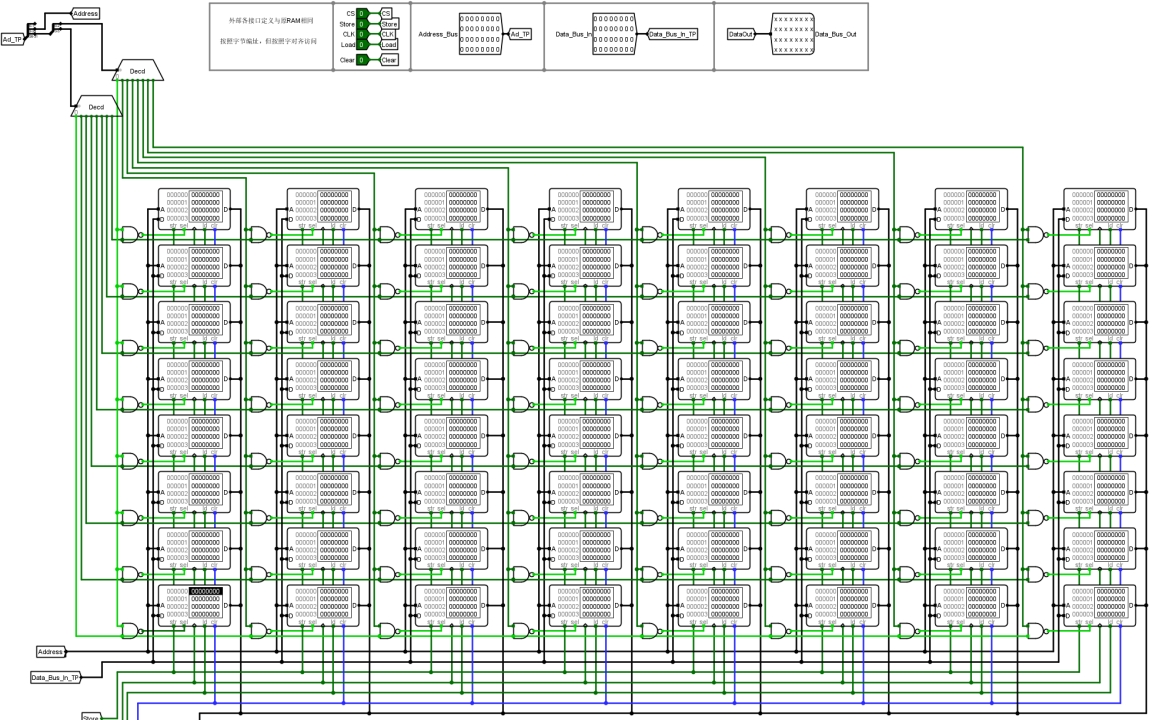

(4).Ram存储阵列的设计

Ram存储器用来当做数据存储器。对于读出指令,ALU的计算结果将连接到数据存储器的地址。从数据存储器中读取的数据将出现在RD上,并在时钟周期结束时写入到寄存器文件中的目的寄存器。我设计的Rom存储阵列由64个rom存储器组成,通过地址的高6位进行片选。

图 22 Ram存储阵列电路

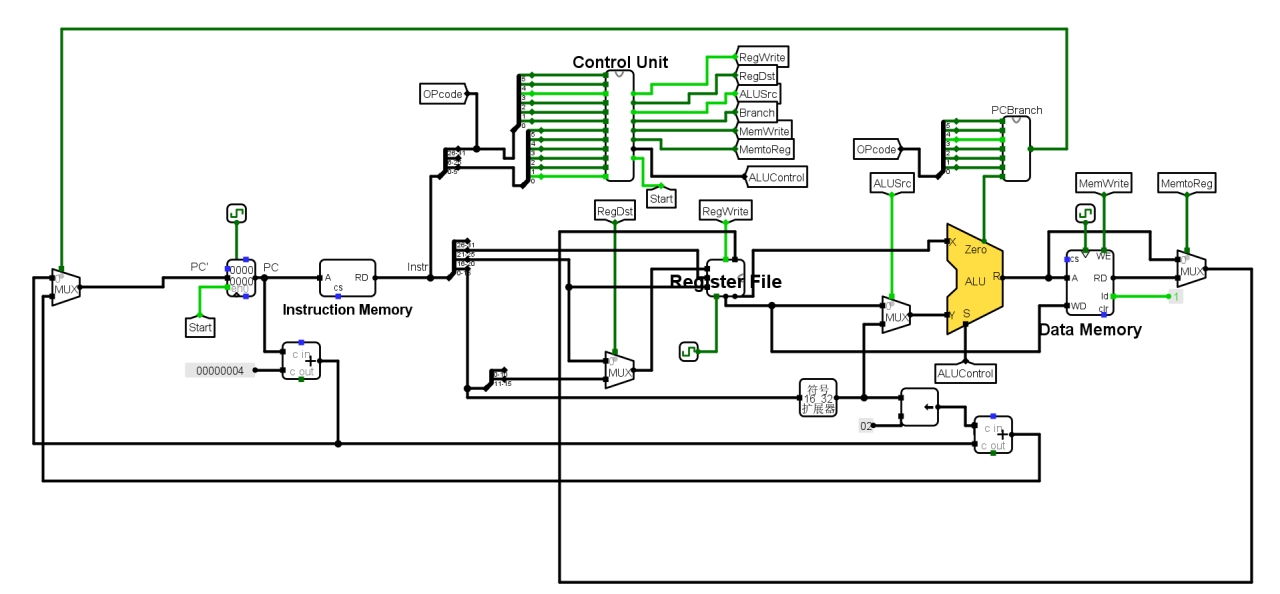

3.2 设计数据通路

设计了有3种类型指令的数据通路,包括R类型、lw、sw、addi、beq和ben指令的数据通路。

在设计数据通路前,需要熟悉了解这三种类型指令的格式。对于以上指令外,我还扩展了系统调用指令syscall。当运行该指令时,终止CPU的运行。

图 23 三种类型指令的格式

| 指令 | 描述 |

|---|---|

| lw | 字载入 |

| sw | 字存储 |

| addi | 立即数加法 |

| beq | 如果相等则跳转 |

| bne | 如果不相等则跳转 |

表 5 指令描述

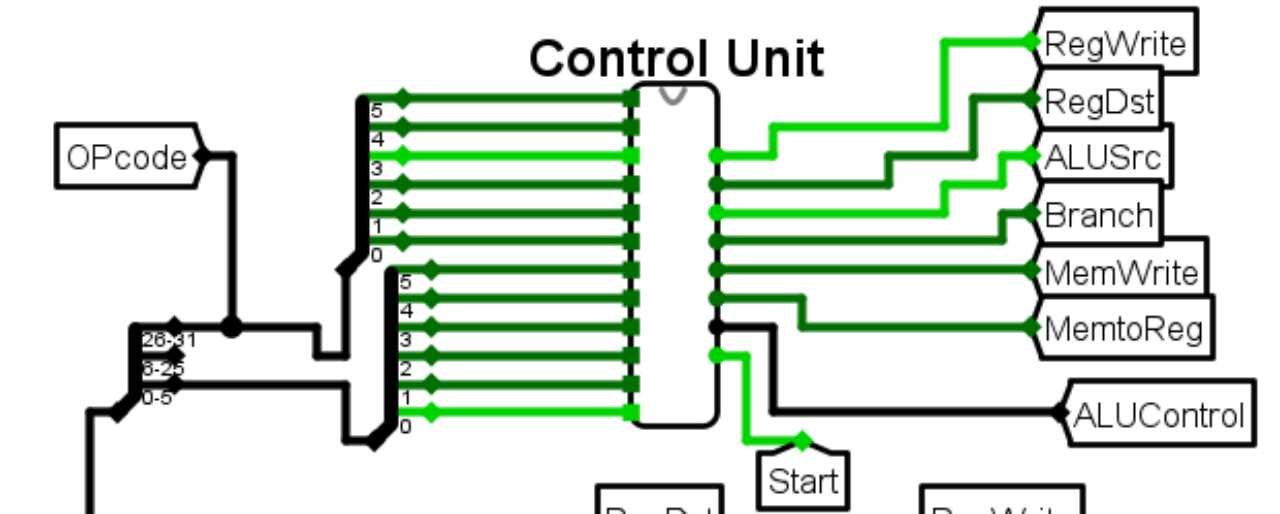

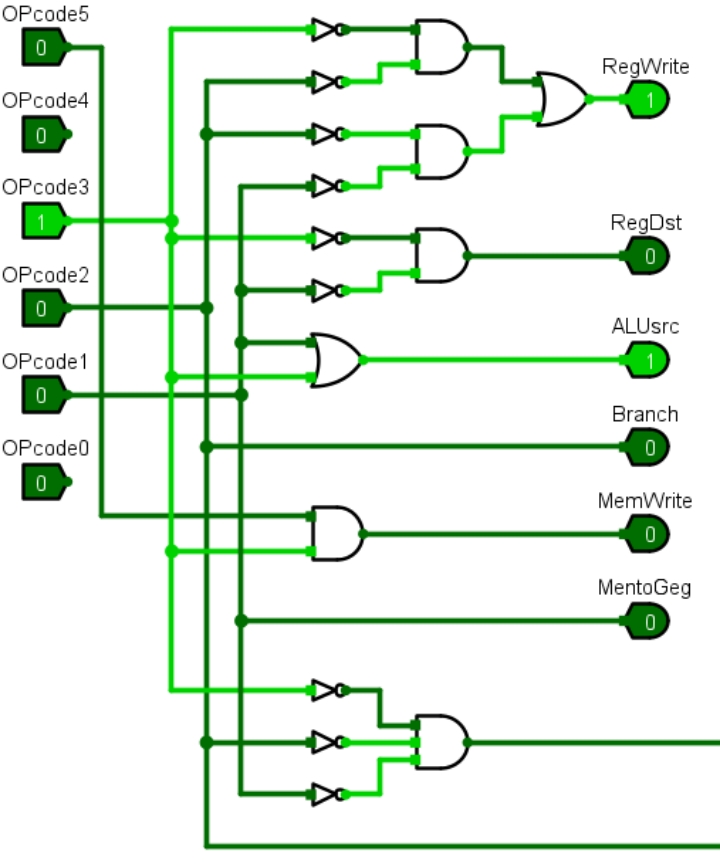

3.3设计控器

对于各种指令不同的数据通路,我设计了控制器输出多个控制信号。控制单元主要分为主译码器和复译码器。控制单元是基于指令中的opcode字段和funct字段计算控制信号。大多数的控制信号来自opcode字段,但是R-类型指令也使用funct字段决定ALU的操作。为了简化组合逻辑,我把控制单元分成了两个组合逻辑部分。如图19所示,主译码器从opcode中计算出大部分的输出信号,同时也会产生一个两位的ALUOP信号,ALU译码器使用ALUOP信号并且结合funct字段计算ALUControl。

所有的R-类型指令使用相同的主译码器值,因为它们的差异仅仅在于ALU译码器的输出。对于所有不需要写入寄存器文件的指令(sw和beq、bne),不必关心RegDst和MemtoReg信号,所以我在真值表中把它们记为X。

图 24 完整的单周期MIPS处理器

图 25 控制器

图 26 主译码器电路

图 27 ALU译码器电路

| ALUOP | funct | ALUControl |

|---|---|---|

| 00 | X | 010 |

| X1 | X | 110 |

| 1X | 100000 | 010 |

| 1X | 100010 | 110 |

| 1X | 100100 | 000 |

| 1X | 100101 | 001 |

| 1X | 101010 | 111 |

图 28 ALU译码器真值表

| 指令 | 操作码 | RegWrite | RegDst | ALUsrc | Branch | MemWrite | MentoReg | ALUOP |

|---|---|---|---|---|---|---|---|---|

| R-类型 | 000000 | 1 | 1 | 0 | 0 | 0 | 0 | 10 |

| lw | 100011 | 1 | 0 | 1 | 0 | 0 | 0 | 00 |

| sw | 101011 | 0 | X | 1 | 0 | 1 | X | 00 |

| beq | 000100 | 0 | X | 0 | 1 | 0 | X | 01 |

| bne | 000101 | 0 | X | 0 | 1 | 0 | X | 01 |

| addi | 001000 | 1 | 0 | 1 | 0 | 0 | 0 | 00 |

图 29 主译码器真值表

| 指令 | 操作码 | ALU-ZERO | PCBranch |

|---|---|---|---|

| beq | 000100 | 0 | 1 |

| bne | 000101 | 1 | 1 |

图 30 PCBranch译码器真值表

| 指令 | funct | Start |

|---|---|---|

| syscall | 000100 | 0 |

| 其他 | 其他 | 1 |

图 31 Start真值表

五.实验结果

5.1 实验1结果

使用计数器循环递增产生0-15的二进制数传送给自己设计的七段译码电路芯片,使用七段数码管显示译码结果。四个电路分别能够实现显示0到9的数字且大于9不显示、显示0到9的数字且大于9显示E、显示0到F的且有极性控制、显示0到F的数字或字母。

图 32 七段数码管译码电路测试结果

5.2 实验2结果

以二进制形式输入乘数和被乘数,计算十进制17×2的结果,测试结果正确。

图 33 基础乘法器测试结果

图 34 快速乘法器测试结果

5.3 实验3结果

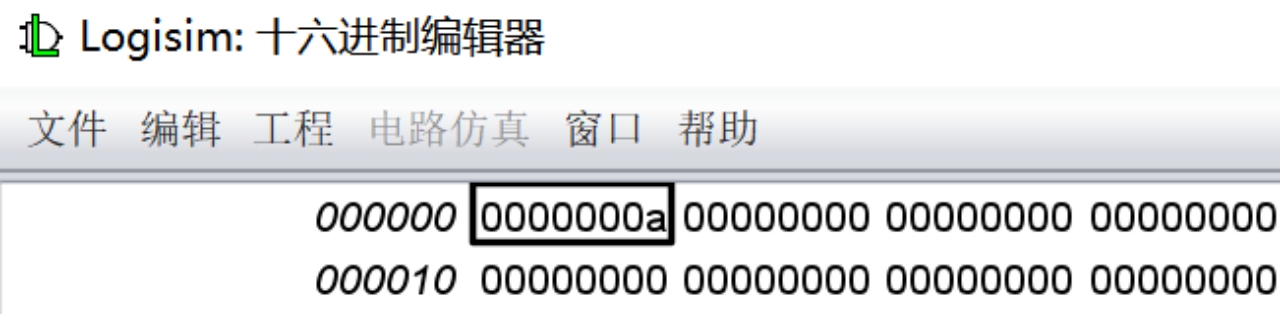

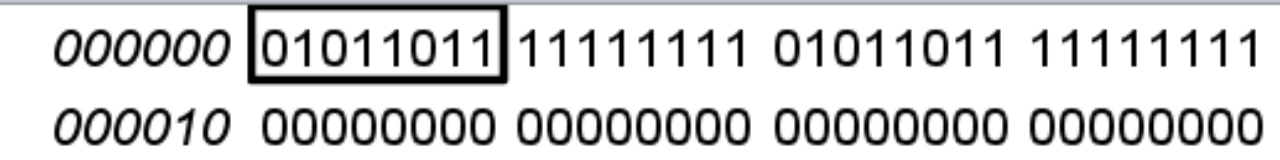

在ROM中装载老师提供的sort.hex测试代码,观察RAM中得到的排序结果,得到的排序结果正确,满足降序排序。

图 35 排序结果

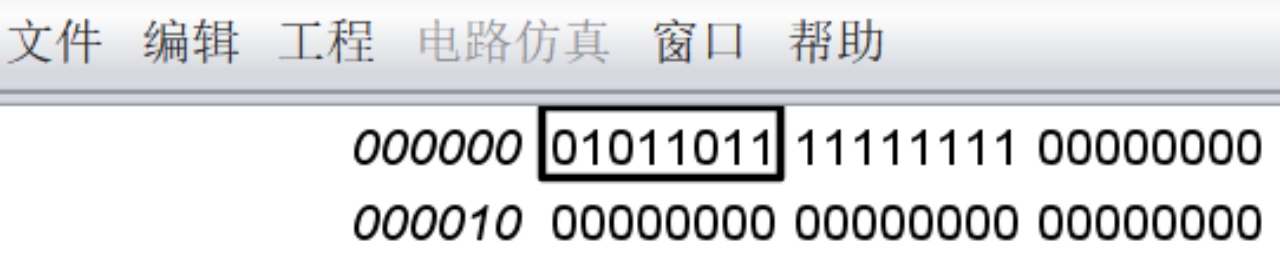

我额外地设计了以下的MIPS指令,用来测试该单周期CPU。

(1)设计测试用例

| 汇编语言 | 机器语言 |

|---|---|

| addi $ s0 ,$ 0 , 10 | 2010000a |

| addi $s1,$0,0 | 20110000 |

| sw s 0 , 0 ( s0,0( s0,0(s1) | ae300000 |

| 汇编语言 | 机器语言 |

|---|---|

| and $ s3 ,$ s1 , $ s2 | 02329824 |

| or $ s4 ,$ s1 , $ s2 | 0232a024 |

(2)测试结果

图 36 用例1测试结果

图 37 用例2输入

图 38 用例2输出

2个测试用例结果正确。

六.实验总结

在这次实验过程中,我对于卡诺图化简逻辑、无关项、乘法器原理、有限状态机和单周期CPU的知识有了更为深入的了解。在设计电路的过程中,不仅仅需要对这些知识熟悉掌握,而且还需要我们有动手实践的能力。这几个实验都是在logisim平台上完成,刚开始上手的时候,会感到有一些不适应,经过这几次实验后,我对于这个软件更加熟悉了解。当然,在实验中我也存在着不足的地方,比如在设计单周期CPU的时候,考虑不够周全,刚开始的时候设计的数据通路没有包括bne指令的,结果在对老师给的代码测试时,发现测试的结果有一些错误,后来我仔细检查了数据通路后,发现缺少了这一指令的数据通路,经过修改完善后,测试结果正常。

我认为可以创新的地方是快速乘法器,我设计的快速乘法器是一次进行两位运算的。但是我在查阅资料的过程中发现,快速乘法器可以实现一次性更多位的运算,比如一次进行3位运算,这样需要考虑的操作可能会更多。但是由于时间的关系,最终没有时间去实现这一创新。

对于这门课程,我的学习过程体验是很好的。课程中安排有实验的内容,并且安排时间给学生上机做实验,这对于深入理解教材中的知识是很有帮助的,对于我们理解计算机的一些底层的逻辑结构和原理很有帮助。姜老师对于课程的设计也很合理,把知识讲解的清晰而且易于理解。教学内容细化且富有层次,设计的思路和方法既向我们传授了知识又具有启发性。对于课程我提出的建议是,希望老师能够多安排这样的实验,比如安排对于高速缓存的设计和虚拟存储器的设计这一方面的实验内容。

总而言之,在这门课程中,教学内容成功融合了数字逻辑和计算机体系结构。介绍了很多数字系统设计的内容,最终引出了计算机体系结构,对于我们如何完美地设计复杂系统提供了很好的指导。

智能推荐

oracle 12c 集群安装后的检查_12c查看crs状态-程序员宅基地

文章浏览阅读1.6k次。安装配置gi、安装数据库软件、dbca建库见下:http://blog.csdn.net/kadwf123/article/details/784299611、检查集群节点及状态:[root@rac2 ~]# olsnodes -srac1 Activerac2 Activerac3 Activerac4 Active[root@rac2 ~]_12c查看crs状态

解决jupyter notebook无法找到虚拟环境的问题_jupyter没有pytorch环境-程序员宅基地

文章浏览阅读1.3w次,点赞45次,收藏99次。我个人用的是anaconda3的一个python集成环境,自带jupyter notebook,但在我打开jupyter notebook界面后,却找不到对应的虚拟环境,原来是jupyter notebook只是通用于下载anaconda时自带的环境,其他环境要想使用必须手动下载一些库:1.首先进入到自己创建的虚拟环境(pytorch是虚拟环境的名字)activate pytorch2.在该环境下下载这个库conda install ipykernelconda install nb__jupyter没有pytorch环境

国内安装scoop的保姆教程_scoop-cn-程序员宅基地

文章浏览阅读5.2k次,点赞19次,收藏28次。选择scoop纯属意外,也是无奈,因为电脑用户被锁了管理员权限,所有exe安装程序都无法安装,只可以用绿色软件,最后被我发现scoop,省去了到处下载XXX绿色版的烦恼,当然scoop里需要管理员权限的软件也跟我无缘了(譬如everything)。推荐添加dorado这个bucket镜像,里面很多中文软件,但是部分国外的软件下载地址在github,可能无法下载。以上两个是官方bucket的国内镜像,所有软件建议优先从这里下载。上面可以看到很多bucket以及软件数。如果官网登陆不了可以试一下以下方式。_scoop-cn

Element ui colorpicker在Vue中的使用_vue el-color-picker-程序员宅基地

文章浏览阅读4.5k次,点赞2次,收藏3次。首先要有一个color-picker组件 <el-color-picker v-model="headcolor"></el-color-picker>在data里面data() { return {headcolor: ’ #278add ’ //这里可以选择一个默认的颜色} }然后在你想要改变颜色的地方用v-bind绑定就好了,例如:这里的:sty..._vue el-color-picker

迅为iTOP-4412精英版之烧写内核移植后的镜像_exynos 4412 刷机-程序员宅基地

文章浏览阅读640次。基于芯片日益增长的问题,所以内核开发者们引入了新的方法,就是在内核中只保留函数,而数据则不包含,由用户(应用程序员)自己把数据按照规定的格式编写,并放在约定的地方,为了不占用过多的内存,还要求数据以根精简的方式编写。boot启动时,传参给内核,告诉内核设备树文件和kernel的位置,内核启动时根据地址去找到设备树文件,再利用专用的编译器去反编译dtb文件,将dtb还原成数据结构,以供驱动的函数去调用。firmware是三星的一个固件的设备信息,因为找不到固件,所以内核启动不成功。_exynos 4412 刷机

Linux系统配置jdk_linux配置jdk-程序员宅基地

文章浏览阅读2w次,点赞24次,收藏42次。Linux系统配置jdkLinux学习教程,Linux入门教程(超详细)_linux配置jdk

随便推点

matlab(4):特殊符号的输入_matlab微米怎么输入-程序员宅基地

文章浏览阅读3.3k次,点赞5次,收藏19次。xlabel('\delta');ylabel('AUC');具体符号的对照表参照下图:_matlab微米怎么输入

C语言程序设计-文件(打开与关闭、顺序、二进制读写)-程序员宅基地

文章浏览阅读119次。顺序读写指的是按照文件中数据的顺序进行读取或写入。对于文本文件,可以使用fgets、fputs、fscanf、fprintf等函数进行顺序读写。在C语言中,对文件的操作通常涉及文件的打开、读写以及关闭。文件的打开使用fopen函数,而关闭则使用fclose函数。在C语言中,可以使用fread和fwrite函数进行二进制读写。 Biaoge 于2024-03-09 23:51发布 阅读量:7 ️文章类型:【 C语言程序设计 】在C语言中,用于打开文件的函数是____,用于关闭文件的函数是____。

Touchdesigner自学笔记之三_touchdesigner怎么让一个模型跟着鼠标移动-程序员宅基地

文章浏览阅读3.4k次,点赞2次,收藏13次。跟随鼠标移动的粒子以grid(SOP)为partical(SOP)的资源模板,调整后连接【Geo组合+point spirit(MAT)】,在连接【feedback组合】适当调整。影响粒子动态的节点【metaball(SOP)+force(SOP)】添加mouse in(CHOP)鼠标位置到metaball的坐标,实现鼠标影响。..._touchdesigner怎么让一个模型跟着鼠标移动

【附源码】基于java的校园停车场管理系统的设计与实现61m0e9计算机毕设SSM_基于java技术的停车场管理系统实现与设计-程序员宅基地

文章浏览阅读178次。项目运行环境配置:Jdk1.8 + Tomcat7.0 + Mysql + HBuilderX(Webstorm也行)+ Eclispe(IntelliJ IDEA,Eclispe,MyEclispe,Sts都支持)。项目技术:Springboot + mybatis + Maven +mysql5.7或8.0+html+css+js等等组成,B/S模式 + Maven管理等等。环境需要1.运行环境:最好是java jdk 1.8,我们在这个平台上运行的。其他版本理论上也可以。_基于java技术的停车场管理系统实现与设计

Android系统播放器MediaPlayer源码分析_android多媒体播放源码分析 时序图-程序员宅基地

文章浏览阅读3.5k次。前言对于MediaPlayer播放器的源码分析内容相对来说比较多,会从Java-&amp;gt;Jni-&amp;gt;C/C++慢慢分析,后面会慢慢更新。另外,博客只作为自己学习记录的一种方式,对于其他的不过多的评论。MediaPlayerDemopublic class MainActivity extends AppCompatActivity implements SurfaceHolder.Cal..._android多媒体播放源码分析 时序图

java 数据结构与算法 ——快速排序法-程序员宅基地

文章浏览阅读2.4k次,点赞41次,收藏13次。java 数据结构与算法 ——快速排序法_快速排序法