DC综合——学习笔记_dc综合 use the link command-程序员宅基地

DC综合——学习笔记

一、DC综合简介

1.1 什么是综合?

概括地说:综合就是把行为级的RTL代码在工艺、面积、时序等约束下转换成对应的门级网表。

综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包 含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑 网络结构的最佳实现方案。即实现在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

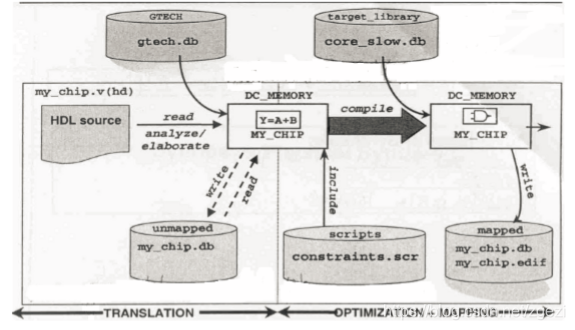

综合主要包括三个阶段:转换(translation)、优化 (optimization)与映射(mapping)。转换阶段综合工具将高层语言描述的电路用门级的逻辑来实现,对于 Synopsys 的综合工具 DC 来说,就是使用 gtech.db1库 中的门级单元来组成 HDL 语言描述的电路,从而构成初始的未优化的电路。优化与映射是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工 艺库上。

- 常用的工具:

Synopsys: DC(用的较多)

Candance:Genus

1.2 综合需要的文件

- RTL文件;

- 标准单元的库文件;

- 其他库文件。如IO库IP库等等(不一定有)

1.3 综合输出的文件

- 综合后的门级网表;

- 带时序约束信息的sdc文件:

- 其他一些后端需要用的特殊配置,如dont_touch设置等;

- 保留综合结果的ddc文件(之后可以直接load这个文件,查看综合结果);

1.4 电路综合的要求

1.4.1 综合脚本的要求

综合脚本必须是可重用的。脚本的可重用主要有两方面的含义:

1)在 整个电路设计过程中,当后端工具提取出线负载模型后作综合或者在布局 布线完成之后再做综合,保证添加的限制条件与初始时的综合是相同的。

2) 当系统的一些参数改变时,比如,一个模块从 16 位变为 32 位,而模块的功能没有改变,可以不改变综合的脚本,只需要改变其中的参数就可以实现该目标。即要保证综合脚本是参数化的。

在添加限制条件时,必须对如下的对象施加限制条件:

1)、电路中需要有时钟的定义一般情况下,希望综合之后的电路是同步的数字电路(异步电路以及模拟电路需要单独处理),而同步电路中都需要设置时钟或者虚拟时钟。

2)、保留时钟网络,不对时钟网络做综合

3)、综合的时候需要指定线负载模型,用于估计连线延迟。

4)、限制模块中组合路径的输入输出延迟。

5)、限制输出的带负载能力(Loading budget)以及输入的驱动单元(driving cell)。 6)、模块同步输出的输出延迟(output delay)的限制,以及同步输入的输入 延迟(input delay)的限制。

7)、多周期路径(multicycle path)以及非法路径(false path)的限制。

8)、工作环境的给定。

1.4.2 综合结果的要求

1)、综合的结果中没有时序违反(timing violation),即综合的结果必须满足时序性能的要求。

2)、综合之后的门级网表必须已经映射到工艺库上。

3)、综合之后的门级网表中应避免包含如下电路结构:

- 在同一个电路中同时含有触发器和锁存器两种电路单元。

- 在电路中出现有反馈的组合逻辑

- 用一个触发器的输出作为另外一个触发器的时钟

- 异步逻辑和模拟电路未单独处理

- 使用的单元电路没有影射到工艺库中

二、DC综合的流程以及分步骤讲解

2.1 DC的启动与退出

两种启动DC方式

- dc_shell:命令行方式,最常用!!!

- design_vision:图形化界面方式(几乎不用)

DC打开时会自动运行当前目录下的.synopsys_dc.setup文件(默认)。一些统一的参数配置等可以写在这个文件里。(但是不是必须的)

脚本可以分步骤运行也可以source一次性运行

把所有的脚本保存成一个tcl文件,当下一次改RTL时,只需要运行这个tcl文件

dc_shell -f top_dc.tcl -output_log_file top_syn.log

- 退出:

以使用 exit 命令来退出 design compiler,使用 图形界面方式时,在 file 菜单下有 quit 按钮可以退出 design analyzer,或者在 design analyzer 的 command window 中输入 exit 也可以。

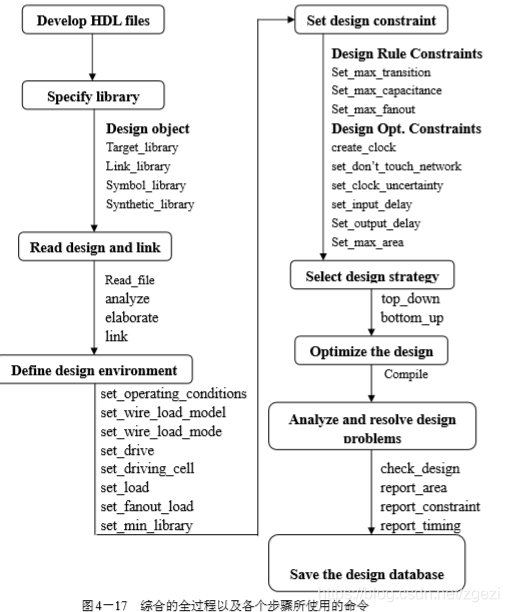

2.2 DC综合流程

综合流程:

- 设置综合环境:推荐参数化环境变量的配置,目录结构的设置,文件的管理,

- 指定综合的库文件:库文件路径,哪些库文件

- 读取RTL:综合工具会对RTL进行转化成布尔表达式,之后再将其映射成门级网表(有错误会报错)

- 设置综合参数:一些综合配置

- 设置约束文件(重要):

- 映射门级单元及优化:

- 替换带scan DFF(可选):将普通的触发器替换成带scan控制的触发器,(现在一般用Tessent加扫描链)

- 检查综合结果并输出报告:

2.2.1 综合流程步骤具体内容

1、设置综合环境:

设置环境变量,如顶层的名字;

创建目录结构,rpt,out等文件夹;

指定临时文件存放目录等;

设置一些自定义命令等;

指定综合库文件

2、指定综合库文件:

设置 search_path, target_library,link_library,symbol_library,(所有的Library文件都是二进制db文件 ,只有工具能够识别,.lib设计者可读)

search_path: 设定好后,综合工具只会从该指定的路径去寻找各种库文件

目标库(target_library):把RTL映射成门级网表式时参考的库文件,一般就是与工艺对应的标准单元库。

target_library 用于设置综合时所要映射的库,target_library 中包含有单元电路的延迟信息,DC 综合时就是根据 target_library 中给出的单元电路的延迟信息来计算路径的延迟。Link_library 与 target_library 是定义了半导体制造商提供的单元电路及其 相关信息的技术库,这些信息包括单元名字、引脚名字、单元延迟信息、引脚 的带负载能力、工作环境等。

链接库(link_library):包含target_library,在此基础上再加上IO库文件,IP库文件等。

注意 :在 link_library 的设置中必须包含’’,* 表示 DC 在引用实例化模块 或者单元电路时首先搜索已经调进DC memory的模块和单元电路,如果在link library 中不包含’’,DC 就不会使用 DC memory 中已有的模块,因此,会出 现无法匹配的模块或单元电路的警告信息(unresolved design reference)。

symbol_library:定义单元显示的图形库,当用design_vision查看图形界面时使用。(没有也没关系)

另外gtech.db和standard.sldb分别包含了GTECH逻辑单元和基本DW。工具会自动加载。

指定前三个就够了,后面的知道就行。

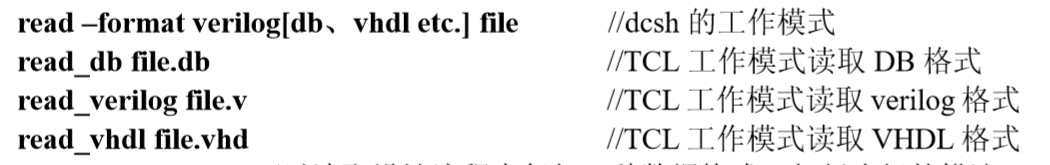

3、读取RTL文件(或网表文件)

读入所有RTL文件后,指定顶层模块并Link(current design)

- 方法1:一个个读取(读100个需要写100次)

read_verilog rtl_file1.v

read_verilog rtl_file2.v - 方法2:一次性读取整个flist (实际中肯定推荐方法2)

analyze -format sverilog -vcs “-f $RTL_FILE/flist.f”

补充:

Design Compiler 可以读取设计流程中任何一种数据格式,如行为级的描述、 RTL 级的描述、门级网表等等,不过由于不同的数据格式使得 Design Compiler 综合的起点不同,即使实现相同的功能,也可能会产生不同的结果。

读取源程序的另外一种方式是配合使用 analyze 命令和 elaborate 命令:

analyze 是分析 HDL 的源程序并将分析产生的中间文件存于 work(用户也可以自 己指定)的目录下;

elaborate则在产生的中间文件中生成verilog的模块或者VHDL 的实体,缺省情况下,elaborate 读取的是 work 目录中的文件。

当读取完所要综合的模块之后,需要使用 link 命令将读到 Design Compiler 存储区中的模块或实体连接起来,如果在使用 link 命令之后,出现 unresolved design reference 的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文 件中添加 link_library,告诉 DC 到库中去找这些模块,同时还要注意 search_path 中的路径是否指向该模块或单元电路所在的目录。

4、设置综合环境

一般是一些比较通用的设置,与设计关系不大;

主要包括编译的一些选项,连线、端口以及模块命名的规范,是否允许使用Latch,是否允许一些assign出现等等。

5、设置约束文件

设置约束文件(综合的核心、优先级从高到低)

- DRC约束

set_max_transition

set_max_fanout (输出最大的负载) - 时序约束(约束的核心)

Create_clock

Set_input_delay

Set_output_delay

…

如果时钟频率需要100M,而设成了1G,就会一直尝试优化,最后在report timing之后会发些1G综合出来的面积可能是1um2,而100M综合出来的面积是0.8um2,频率设高了面积会变大,至于怎么优化是由designer决定。 - 面积约束(实际用处不大)

set_max_area

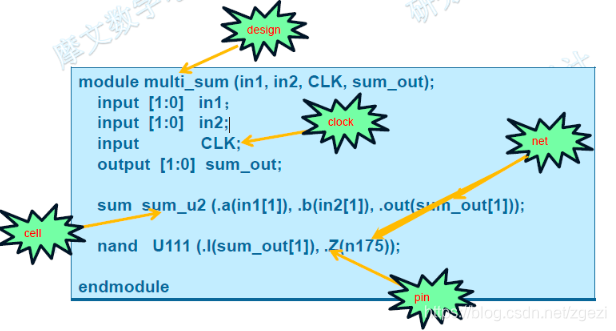

get_design 拿到module的名字,get_clock 拿到所创建的clock get_pins实例化后里面的端口如(.a, .b, out) get_ports当前模块的端口如in1,in2,CLK 因此,pin与port是相对而言的。get_net得到线的名字不在当前port上又在当前这层就是个线。 get cell得到的实例化后的名字如sum_u2 U111。

具体:

1、设计规则限制DRC:

设计规则的限制是在技术库中给定的,这些设计规则是由 vendor 提供的,为 了保证电路在制造之后能够正确的工作而设定的,因此,这些规则是不能够违反 的,而且用户不能将这些设计规则的限制条件取消掉,不过用户在使用时可以根据要求设置更加严格的设计规则。DC 综合的时候一定要满足这些条件,否则电 路在制造时就没有保证。主要有以下几个命令

- set_max_capacitance :

用于设置输出单元允许的电容负载。 - set_max_transition: transition time 是指电压从 10%VDD 上升到 90%VDD 所需要的时间,或者是从 90%VDD 下降到 10%VDD 所需要的时间。从理论上来说,只要输入 电平变化了,不管输出带了多大的负载,经过一段时间,总是能够使输出电 平变化的,但是上升或下降时间长就意味着电路的速度很慢。输出的 transition time 和输入的 transition time 以及输出负载有关。

- set_max_fanout: 设置允许的最大等效负载 如果在库中定义了这些设计规则,用户同时也设置了这些规则,DC 在优化 的时候则满足限制较严格的规则。

2、电路优化的限制:

-

create_clock :

在电路综合的过程中,所有时序电路以及组合电路的优化都是以时钟为 基准来计算路径延迟的,因此,一般都要在综合的时候指定时钟,作为估计路径延迟的基准。

create_clock 命令的格式为 create_clock –name clk_name –period cycle_value –waveform edge_list

命令使用要点:

1) 定义一个时钟,该时钟域(clock domain)中的所有的同步电路都以该时钟为基准。

2) 定义时钟时可以不指定时钟源(source pin or port),此时必须指定时钟名,该时钟为 虚拟时钟(Virtual Clock), 在实际的电路中没有对应的 clock port or clock net。主要 是用于作为电路中输入到输出的组合逻辑电路的时钟基准。

3) 定义好 Clock 之后,为了模拟实际的时钟,可以用 set_clock_uncertainty 来指定实 际时钟网络的 clock_skew。

4) 由于布局布线时会对时钟网络重新进行优化,因此,在综合的时候无需考虑时钟 网络上的大负载,即不用在综合的时候在时钟网络上加 buffer 来驱动。使用 set_dont_touch_network 命令来实现

5) create_clock 同时也定义了时钟的波形,-waveform 的选项是用于指定上升沿和下 降沿的时刻。可以在一个时钟周期中定义多个时钟脉冲。

6) 定义好时钟之后,缺省情况下会产生一个路径组(path group),即以该时钟为路 径终点的所有路径都属于该路径组。

7) 对于 RISC_CORE,要求设置电路的工作频率为 250MHz,因此时钟周期为 4ns,

使用命令如下: create_clock –period 4 –name core_clk [get_ports clk] 命令成功执行,DC 返回为 1。

使用 create_clock 产生一个时钟之后,需要用 set_clock_uncertainty 命令来模拟时钟 偏移,对于 RISC_CORE 的实例,使用的命令如下: set_clock_uncertainty 0.3 [get_clocks core_clk] 命令成功执行,DC 返回为 1。 -

set_dont_touch_network

由于时钟信号是驱动大负载的。在综合的时候综合工具会对负载进行估 计,从而在该网络上加上一些有足够驱动能力的 buffer 或者反相器,以使得电路的上升时间和下降时间能够满足要求。而前端工具无法知道连线的走向和长度,在估计时钟网络的负载时不准确,而且 floorplan 的结果将会 影响连线的长度,从而影响连线的负载,因此,前端工具不对大负载的网络进行处理,而把这个工作留到后端。所以在综合的时候需要告诉综合工具不对时钟网络进行处理。

命令的格式: set_dont_touch_network clk_name

命令的使用要点:

1) 指定在综合的过程中不对时钟网络进行优化,一般还需要设置此属性的还有 reset 信号,enable 信号,test_clock 信号等

2) 对时钟设置此属性时,不能使用 set_dont_touch 命令,因为布线完成之后,会对时 钟线重新命名,使用 set_don’t_touch 会在布线之后的综合中找不到重新命名后的 net。(注:set_dont_touch 一般用于设置 cell or instance 的属性,使 DC 不对该 cell or instance 进行优化)

3) dont_touch 的对象是触发器时钟端之前的网络,

4) 对于 RISC_CORE,也需要对时钟设置 dont_touch,使用如下命令: set_don’t_touch_network [get_clocks core_clk] 命令成功执行时,DC 返回的值为 1。 -

set_dont_touch

用于指定不需要综合工具进行优化的对象,这些对象有单元电路、 子模块、硬核等,使得在综合的时候综合工具可以忽略施加在这些对象 上的限制条件。 -

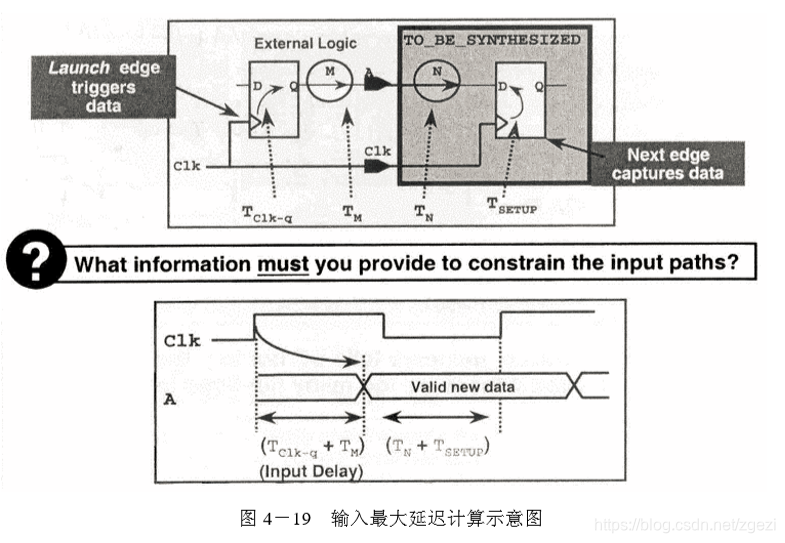

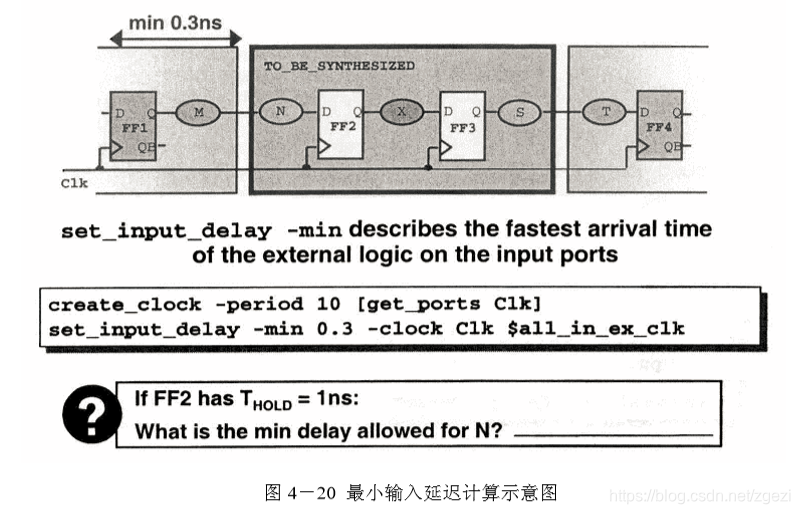

set_input_delay

当一条路径跨越模块边界时,需要将整条路径允许的延迟在两个模块之 间分配,该命令定义输入信号允许的到达时间。

命令的格式: set_input_delay –clock clk_name –max max_value –min min_value –add_delay

命令使用要点:

1) setup time 和 hold time :这两个参数都是在工艺库中给定的。Setup time 是指时序 单元电路数据端比时钟端有效沿提前到达的最少时间。Hold time 是指时钟有效边 沿之后数据至少需要保持的时间。这两个参数都是物理上的要求,为了使数据信 号能够被正确读取。

2) -max 的选项:指定输入的最大延迟,为了满足时序单元建立时间(setup time) 的要求。

3) -min 的选项:指定输入的最小延迟,为了满足时序单元保持时间(hold time) 的要求。

4) 输入延迟的计算: 路径的最大输入延迟是限制信号到达的最晚时刻

5) 对于 RISC_CORE 的实例,只给出了最大延迟的指标,即输入的最大延迟为 1.5ns,

使用如下命令: set_input_delay –max 1.5 –clock core_clk [remove_from_collection [all_inputs] [get_ports Clk]]

由于优化时不针对时钟网络,因此,在施加限制条件时必须将时钟端从限制的 对象中移去。该命令成功执行,则 DC 返回为 1。 -

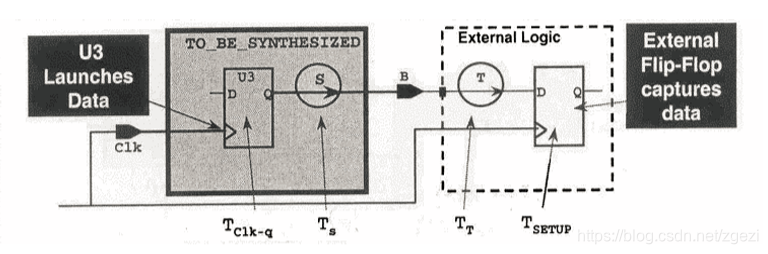

set_output_delay

该命令类似与 set_input_delay,定义输出信号要求的到达时间

命令的格式: set_output_delay –clock clk_name –max max_value –min min_value -add_delay

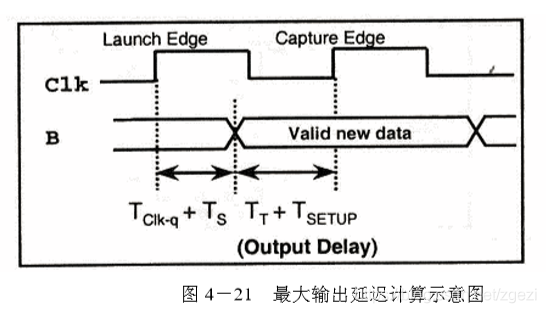

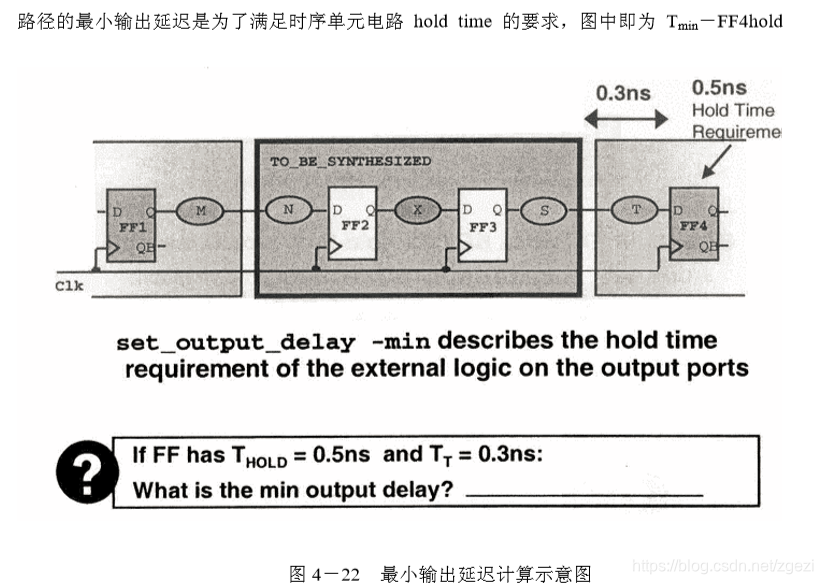

输出延迟的计算: 路径的最大输出延迟是综合对象外部组合路径的延迟之和,即 TT+Tsetup, 如图所示

对于 RISC_CORE 的实例,需要设置的输出延迟只要设置最大延迟,其延 迟值为 1.5ns。

使用的命令如下: set_output_delay –max 1.5 –clock core_clk [all_inputs] 若命令成功执行,则 DC 的返回值为 1。 -

set_max_area

因为芯片面积直接关系到芯片的成本,面积越大,成本越高,因此, 集成电路的设计总是希望面积尽量小,以减小芯片成本。该命令用于限 制综合的面积。

命令的格式: set_max_area area_value

命令使用要点:

1) 指定 DC 面积的综合目标。此处的面积为等效的面积,可以定义为两输入的与非门,管子,或者实际的面积。具体的由 Vendor 提供。

2) 可以将 max_area 设置为 0,此时综合后的电路肯定不能满足要求,但 DC 会尽量 对电路的面积进行优化,达到可能的最小面积,但同时也使得综合后的电路没有 “弹性”

3) 对于 RISC_CORE 的电路,其电路的规模约为 50-60Kgates,设置其面积的限制 为 50000,

使用如下命令: set_max_area 50000 若命令成功执行,则返回值为 1。 -

set_max_delay / set_min_delay

如果电路完全是组合逻辑电路,而没有时钟,可以使用这两条命令直接 限制路径的最大最小的延迟。

例如,限制一个 reset 信号:由于 reset 信号跨越了不同的模块,因此, 一般在顶层模块中对该模块做限制: set_max_delay 5 –from reset 即指定所有 reset 信号出发的路径的最大延迟都为 5 限制一个从 IN 输入到 OUT 输出的最小路径: set_min_delay 10 –from IN –to OUT -

set_false_path

以上的命令都是针对同步电路的限制。因为异步电路的时序关系是由协议保证的,即用户在设计电路时就要保证电路能够正常工作。但是,在综合 的时候,用户必须指出电路中跨越异步电路的路径,以便在优化的时候会忽略该路径。 set_false_path 命令用于给出异步电路或者逻辑上不存在的电路,优化的 时候所有加在该路径上的限制条件都不予以考虑。如果要取消该设置,使用 reset_path 命令。

1)指出电路逻辑上不存在的路径: set_false_path –from write_en –to read_en

2)指出异步电路的路径: 如图,由于 CLKA 和 CLKB 是属于不同的时钟晶振,因此,CLKA 到 CLKB 的路径是异步电路。 set_false_path –from [get_clocks CLKA] –to [get_clocks CLKB]

6、映射门级单元及优化

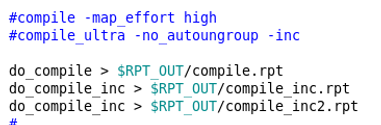

通过compile把RTL映射成门级网表同时优化里面的逻辑。(一般compile执行2到3次)

一般在compile完成后可以用-inc在compile基础上进一步优化

可以用complie_ultra(超级compile)更进一步优化。但是需要额外licence

7、替换带scan触发器

在使用compile时加上-scan参数则会把所有的触发器替换成带sacn端口的触发器(现在一般用Tessent加扫描链);

主要为DFT做准备;

一般会增大20%-30%(经验值);

8、检查综合结果并输出报告

- 用check_design检查设计中是否存在其他隐患问题

- 用check_timing检查设计中是否有路径没有被约束,每一条路径都应该约束到,如果真的有哪一条不需要约束也应该设置成false path。

- 用report_qor查看整体综合后的summary结果

- 用report_area查看综合后得到的面积

- 用report_timing查看具体的setup/hold时序信息。

- 用write_file -f verilog写出综合后的网表文件给后端

- 用write_file -f ddc保存当前综合的数据data base。下次可以直接load后查看结果。不需要重新综合。

- 用write_sdf写出综合后的sdf文件。

- 综合后的sdf没有什么太大的意义,因为时钟网络是理想的,并且也不需要修hold

- 最差的时序才是critical path

- set_critical_path对次关键路径优化

补充:

电路综合完成之后,可以用 report 命令将电路的一些信息 report 出来分 析,阅读报告时主要需要注意几个部分:

1)、看看报告中的综合库、线负载模型、工作条件等是不是你所要求的。

2)、看看报告的路径是最大路径还是最小路径,即看报告中的 Path type 为 max,该路径是为了满足 library 中 FF 的 setup time 的要求。

3 )、看路径中是否有很大延迟的单元,或者输入/输出延迟是否很大

4 )、看关键路径上是否有 slack

5)、这样综合完成之后,对于最差工作环境下的库如果没有问题,对于最好 的工作情况,可能会出现 Hold time violation. 这时可用 set_fix_hold [all_clocks],之后再 compile, 来让 DC 对电路中的 hold time violation 进行 处理。

6)、如果在综合之后发现电路中出现 violation,即电路的时序不能满足要求,

当出现的 slack 比较小时,可以使用一些综合的选项来减小这些 slack; 如果 slack 比较大,通过综合的这些选项无法解决,则需要返回重新写 HDL 源代码。 一般在综合时 violation 较小时,可以用 compile –inc –map high 来减小路 径的延迟。

具体实例

初始目录结构:

script:存放dc综合脚本;

source_file:存放设计.v文件;

set SCRIPT_FILE script

source ./$SCRIPT_FILE/set_env.tcl

source -echo ./$SCRIPT_FILE/file_create.tcl

set cache_write WORK/$file_version

set cache_read WORK/$file_version

# set CMP_OPTION "-no_autoungroup -scan"

if {

$do_scan == 1} {

set CMP_OPTION [format "%s %s" -no_autoungroup -scan]

} else {

set CMP_OPTION [format "%s" -no_autoungroup]

}

set compile_cmd "compile $CMP_OPTION"

alias do_compile $compile_cmd

alias do_compile_inc $compile_cmd -inc

set search_path [list \

./ \

../ \

/home/ZhengZhq/fab/synopsys90nm_lib/stdcel/db/ss1p08v125c \

]

set target_library [list ${lib_slow}.db]

set link_library [list "*" ${

lib_slow}.db]

#set synthetic_library [list standard.sldb]

#set symbol_library [list generic.sdb]

define_design_lib WORK -path ./WORK/$file_version

##################################################################

## Read in Verilog Files ##

##################################################################

# read_sverilog ./$RTL_FILE/ram_dual.v

# read_sverilog ./$RTL_FILE/fifo_512x10.v

# current_design $working_design

# link

#analyze -format sverilog -vcs "-f $RTL_FILE/flist.f"

analyze -format sverilog -vcs -f ./source_file/plus_pipe.v

elaborate $working_design

report_attributes -design

current_design $working_design

link

source -echo ./$SCRIPT_FILE/set_parameter.tcl

source -echo ./$SCRIPT_FILE/constraint_sdc.tcl

source -echo ./$SCRIPT_FILE/dont_touch.tcl

#change naming rule

report_clock > $RPT_OUT/clock.syn.rpt

report_clock -skew >> $RPT_OUT/clock.syn.rpt

current_design $working_design

uniquify -force

##################################################################

## Optimization

##################################################################

change_names -rules verilog -hierarchy

# there is no supprot of compile_ultra,so use compile

compile > $RPT_OUT/compile.rpt

compile -inc > $RPT_OUT/compile_inc.rpt

compile -inc > $RPT_OUT/compile_inc1.rpt

#do_compile > $RPT_OUT/compile.rpt

#do_compile_inc > $RPT_OUT/compile_inc.rpt

#do_compile_inc > $RPT_OUT/compile_inc2.rpt

#

change_names -rules verilog -hierarchy

current_design $working_design

##########################################

check_design > $RPT_OUT/check_design.rpt

check_timing > $RPT_OUT/check_timing.rpt

report_qor > $RPT_OUT/qor.rpt

report_area > $RPT_OUT/area.rpt

report_area -hierarchy > $RPT_OUT/area_hier.rpt

report_timing -loops > $RPT_OUT/timing_loop.rpt

report_timing -path full -net -cap -input -tran -delay min -max_paths 200 -nworst 200 > $RPT_OUT/timing.min.rpt

report_timing -path full -net -cap -input -tran -delay max -max_paths 200 -nworst 200 > $RPT_OUT/timing.max.rpt

report_constraints -all_violators -verbose > $RPT_OUT/constraints.rpt

report_power > $RPT_OUT/power.rpt

###################################################################

## Saving Hierarchy

###################################################################

set bus_naming_style {

%s[%d]}

write_file -f verilog -hierarchy -output $DATA_OUT/$working_design.v

write_sdf -version 2.1 $DATA_OUT/$working_design.sdf

write_file -f ddc -hierarchy -output $DATA_OUT/$working_design.ddc

write_sdc $DATA_OUT/$working_design.sdc

#exit

1、设置综合环境:

set RTL_FILE source_file

set working_design plus_pipe

set file_version dc_v1

set do_scan 0

set RPT_DIR RPT

set OUT_DIR OUT

set RPT_OUT [format "%s%s" $RPT_DIR/ $file_version]

set DATA_OUT [format "%s%s" $OUT_DIR/ $file_version]

set lib_slow saed90nm_max_hth

set lib_fast saed90nm_min_ht

set lib_typ saed90nm_typ

创建目录结构:

if {

[file exist $RPT_DIR]} {

echo "File $RPT_DIR already exist"

} else {

exec mkdir $RPT_DIR

echo "Creating $RPT_DIR !!!"

}

if {

[file exist $RPT_DIR/$file_version]} {

echo "File $file_version already exist"

exec rm $RPT_DIR/$file_version -r

exec mkdir $RPT_DIR/$file_version

echo "Re-create $file_version files"

} else {

exec mkdir $RPT_DIR/$file_version

echo "Creating $file_version in $RPT_DIR !!!"

}

if {

[file exist $OUT_DIR]} {

echo "File $OUT_DIR already exist"

} else {

exec mkdir $OUT_DIR

echo "Creating $OUT_DIR !!!"

}

if {

[file exist $OUT_DIR/$file_version]} {

echo "File $file_version already exist"

exec rm $OUT_DIR/$file_version -r

exec mkdir $OUT_DIR/$file_version

echo "Re-create $file_version files"

} else {

exec mkdir $OUT_DIR/$file_version

echo "Creating $file_version in $OUT_DIR !!!"

}

# create work

if {

[file exist WORK]} {

echo "File WORK already exist"

} else {

exec mkdir WORK

echo "Creating WORK!!!"

}

if {

[file exist WORK/$file_version]} {

echo "File WORK/$file_version already exist"

} else {

exec mkdir WORK/$file_version

echo "Creating WORK/$file_version in WORK !!!"

}

OUT:存放输出文件

RPT:存放报告

WORK:存放临时文件

2、设置综合库文件

set search_path [list \

./ \

../ \

/home/ZhengZhq/fab/synopsys90nm_lib/stdcel/db/ss1p08v125c \

]

set target_library [list ${lib_slow}.db]

set link_library [list "*" ${

lib_slow}.db]

3、读取RTL文件(或网表文件)

##################################################################

## Read in Verilog Files ##

##################################################################

# read_sverilog ./$RTL_FILE/plus_pipe.v

# current_design $working_design

# link

#analyze -format sverilog -vcs "-f $RTL_FILE/flist.f"

analyze -format sverilog -vcs -f ./source_file/plus_pipe.v

elaborate $working_design

report_attributes -design

current_design $working_design

link

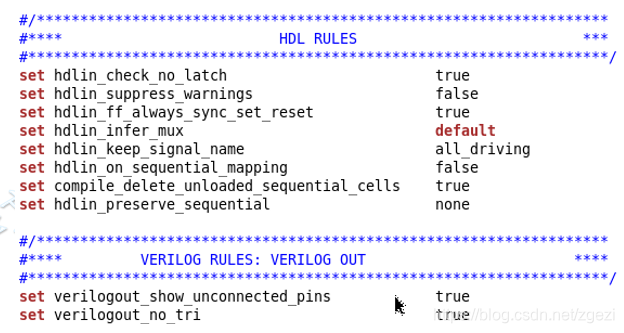

4、设置综合环境

set_parameter.tcl

##################################################################

## Compile variable##

##################################################################

set write_name_nets_same_as_ports true

set compile_assume_fully_decoded_three_state_buses true

set verilogout_no_tri true

set compile_no_new_cells_at_top_level false

set compile_preserve_sync_resets true

## Remove assign statements when generating gate level netlist

set compile_fix_multiple_port_nets true

# for async reset timing check

set enable_recovery_removal_arcs true

set_fix_multiple_port_nets -all -buffer_constants

#set_fix_multiple_port_nets -all

#/******************************************************************

#**** HDL RULES ***

#*******************************************************************/

set hdlin_check_no_latch true

set hdlin_suppress_warnings false

set hdlin_ff_always_sync_set_reset true

set hdlin_infer_mux default

set hdlin_keep_signal_name all_driving

set hdlin_on_sequential_mapping false

set compile_delete_unloaded_sequential_cells true

set hdlin_preserve_sequential none

#/******************************************************************

#**** VERILOG RULES: VERILOG OUT ****

#*******************************************************************/

set verilogout_show_unconnected_pins true

set verilogout_no_tri true

set verilogout_single_bit false

set verilogout_equation false

#/******

#/******************************************************************

#**** Scan Options ***

#*******************************************************************/

set insert_test_design_naming_style "%s_%d"

#set test_scan_in_port_naming_style "SI%s%s"

#set test_scan_enable_port_naming_style "SCN%s"

#set test_scan_out_port_naming_style "SO%s%s"

5、设置约束条件

set compile_enable_constant_propagation_with_no_boundary_opt false

set timing_enable_multiple_clocks_per_reg true

set enable_recovery_removal_arcs true

create_clock -name CLK_IN -p 10 [get_ports CLK_IN] -waveform {

0 5}

set_max_transition 1.0 [current_design]

set_max_transition -clock_path 0.90 [all_clocks]

set_clock_transition 0.9 [all_clocks]

set_input_transition 0.89 [all_inputs]

set_driving_cell -lib_cell NBUFFX2 -pin Z -no_design_rule [all_inputs]

set_load [load_of ${lib_slow}/NBUFFX2/INP] [all_outputs]

#set_load 0.02 [all_outputs]

#set_load 0.006484 [all_outputs]

set_input_delay 3 -clock CLK_IN [all_inputs]

set_input_delay -max 5 -clock CLK_IN {

PLUS_A PLUS_B}

set_input_delay -min 2 -clock CLK_IN {

PLUS_A PLUS_B}

set_output_delay 1 -clock CLK_IN {

COUT SUM_OUT}

#set_multicycle_path -setup 2 -from A -to B

#set_multicycle_path -hold 1 -from A -to B

# false path

set_false_path -from [get_ports RST]

dont_touch.tcl

# set_dont_touch [get_cells ram_dual/**]

6、映射门级单元和优化

##################################################################

## Optimization

##################################################################

change_names -rules verilog -hierarchy

# there is no supprot of compile_ultra,so use compile

compile > $RPT_OUT/compile.rpt

#do_compile > $RPT_OUT/compile.rpt

#do_compile_inc > $RPT_OUT/compile_inc.rpt

#do_compile_inc > $RPT_OUT/compile_inc2.rpt

#

change_names -rules verilog -hierarchy

current_design $working_design

7、替换带scan触发器

8、检查综合结果并输出报告

check_design > $RPT_OUT/check_design.rpt

check_timing > $RPT_OUT/check_timing.rpt

report_qor > $RPT_OUT/qor.rpt

report_area > $RPT_OUT/area.rpt

report_area -hierarchy > $RPT_OUT/area_hier.rpt

report_timing -loops > $RPT_OUT/timing_loop.rpt

report_timing -path full -net -cap -input -tran -delay min -max_paths 200 -nworst 200 > $RPT_OUT/timing.min.rpt

report_timing -path full -net -cap -input -tran -delay max -max_paths 200 -nworst 200 > $RPT_OUT/timing.max.rpt

report_constraints -all_violators -verbose > $RPT_OUT/constraints.rpt

report_power > $RPT_OUT/power.rpt

###################################################################

## Saving Hierarchy

###################################################################

set bus_naming_style {

%s[%d]}

write_file -f verilog -hierarchy -output $DATA_OUT/$working_design.v

write_sdf -version 2.1 $DATA_OUT/$working_design.sdf

write_file -f ddc -hierarchy -output $DATA_OUT/$working_design.ddc

write_sdc $DATA_OUT/$working_design.sdc

最终得到的文件和报告:

OUT:

ddc文件:保留综合结果的ddc文件(之后可以直接load这个文件,查看综合结果);

sdc(Synopsys design constraints.)文件:时序约束信息文件,用于布局布线

sdf(Standard Delay Format)文件:标准延时格式,用于静态分析和后仿

.v文件:综合后的门级网表(可进一步给PT做STA)

DC综合后的网表.v文件可以拿来做仿真(不带sdf的后仿),(需要model文件和综合后的网表文件,因为RTL被替换成标准单元库了所以需要model文件)。理论上结果是应该要是正确的。

需要加两个参数:+nospecify +notimingcheck

综合后的网表一般setup time是满足的但没有对hold time优化,所以可能有问题。

vcs -fsdb +nospecify +notimingcheck ….

RPT:

如何检查综合结果

- 看运行过程的log是否有报错

- 看各命令打出的报告。检查报告中是否有错误。时序是否收敛,timing是否都通过了,是否有没有约束的端口。

- 打开生成的门级网表,大致检查是否有错误

- 用形式验证工具把生成的网表和RTL做形式验证。确保综合后网表功能正确。(形式验证工具用纯数学的方法比较RTL 和 Netlist是否一样。)

compiler.rpt

Warning: Ignoring compile_fix_multiple_port_nets = TRUE. (UIO-60)

Information: Evaluating DesignWare library utilization. (UISN-27)

============================================================================

| DesignWare Building Block Library | Version | Available |

============================================================================

| Basic DW Building Blocks | K-2015.06-DWBB_201506.0 | * |

| Licensed DW Building Blocks | | |

============================================================================

Information: There are 1 potential problems in your design. Please run 'check_design' for more information. (LINT-99)

Beginning Pass 1 Mapping

------------------------

Processing 'plus_pipe'

Updating timing information

Information: Updating design information... (UID-85)

Beginning Implementation Selection

----------------------------------

Processing 'plus_pipe_DW01_add_0'

Processing 'plus_pipe_DW01_add_1'

Processing 'plus_pipe_DW01_add_2'

Processing 'plus_pipe_DW01_add_3'

Beginning Mapping Optimizations (Medium effort)

-------------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:02 18609.7 1.15 3.5 185.0

0:00:02 18609.7 1.15 3.5 185.0

0:00:02 18609.7 1.15 3.5 185.0

0:00:02 18609.7 1.15 3.5 185.0

0:00:02 18609.7 1.15 3.5 185.0

0:00:02 14824.7 1.15 3.5 0.0

0:00:02 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.15 3.4 0.0

Beginning Delay Optimization Phase

----------------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:03 14661.6 1.15 3.4 0.0

0:00:03 14661.6 1.13 3.4 0.0

0:00:03 14661.6 1.13 3.4 0.0

Beginning Area-Recovery Phase (cleanup)

-----------------------------

TOTAL

ELAPSED WORST NEG SETUP DESIGN

TIME AREA SLACK COST RULE COST ENDPOINT

--------- --------- --------- --------- --------- -------------------------

0:00:03 14661.6 1.13 3.4 0.0

0:00:03 14661.6 1.13 3.4 0.0

0:00:03 14650.3 1.13 3.4 0.0

0:00:03 14638.9 1.13 3.4 0.0

0:00:03 14627.6 1.13 3.4 0.0

0:00:03 14616.3 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

0:00:03 14604.9 1.13 3.4 0.0

Loading db file '/home/XXX/fab/synopsys90nm_lib/stdcel/db/ss1p08v125c/saed90nm_max_hth.db'

Note: Symbol # after min delay cost means estimated hold TNS across all active scenarios

Optimization Complete

---------------------

1

qor.rpt

****************************************

Report : qor

Design : plus_pipe

Version: K-2015.06

Date : Sun Aug 30 15:10:51 2020

****************************************

Timing Path Group 'CLK_IN'

-----------------------------------

Levels of Logic: 20.00

Critical Path Length: 4.86

Critical Path Slack: 0.01

Critical Path Clk Period: 10.00

Total Negative Slack: 0.00

No. of Violating Paths: 0.00

Worst Hold Violation: 0.00

Total Hold Violation: 0.00

No. of Hold Violations: 0.00

-----------------------------------

Cell Count

-----------------------------------

Hierarchical Cell Count: 4

Hierarchical Port Count: 212

Leaf Cell Count: 721

Buf/Inv Cell Count: 192

Buf Cell Count: 38

Inv Cell Count: 154

CT Buf/Inv Cell Count: 0

Combinational Cell Count: 365

Sequential Cell Count: 356

Macro Count: 0

-----------------------------------

Area

-----------------------------------

Combinational Area: 3626.495977

Noncombinational Area: 11483.136185

Buf/Inv Area: 1127.116819

Total Buffer Area: 219.34

Total Inverter Area: 907.78

Macro/Black Box Area: 0.000000

Net Area: 614.463091

-----------------------------------

Cell Area: 15109.632162

Design Area: 15724.095253

Design Rules

-----------------------------------

Total Number of Nets: 903

Nets With Violations: 0

Max Trans Violations: 0

Max Cap Violations: 0

-----------------------------------

Hostname: IC

Compile CPU Statistics

-----------------------------------------

Resource Sharing: 0.10

Logic Optimization: 0.06

Mapping Optimization: 0.46

-----------------------------------------

Overall Compile Time: 1.46

Overall Compile Wall Clock Time: 7.75

--------------------------------------------------------------------

Design WNS: 0.00 TNS: 0.00 Number of Violating Paths: 0

Design (Hold) WNS: 0.00 TNS: 0.00 Number of Violating Paths: 0

--------------------------------------------------------------------

1

report_timing:

Operating Conditions: WORST Library: saed90nm_max_hth

Wire Load Model Mode: enclosed

Startpoint: PLUS_A[0] (input port clocked by CLK_IN)

Endpoint: s1_pre3_reg_15_

(rising edge-triggered flip-flop clocked by CLK_IN)

Path Group: CLK_IN

Path Type: max

Des/Clust/Port Wire Load Model Library

------------------------------------------------

plus_pipe 16000 saed90nm_max_hth

plus_pipe_DW01_add_5

8000 saed90nm_max_hth

Point Incr Path

--------------------------------------------------------------------------

clock CLK_IN (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

input external delay 5.00 5.00 r

PLUS_A[0] (in) 0.01 5.01 r

add_100/A[0] (plus_pipe_DW01_add_5) 0.00 5.01 r

add_100/U195/QN (NAND2X2) 0.48 5.49 f

add_100/U28/ZN (INVX0) 0.92 6.41 r

add_100/U40/QN (NAND2X0) 0.09 6.50 f

add_100/U45/QN (NAND2X0) 0.10 6.60 r

add_100/U44/QN (NAND2X0) 0.10 6.70 f

add_100/U41/QN (NAND2X0) 0.10 6.81 r

add_100/U33/QN (NAND2X0) 0.11 6.91 f

add_100/U29/ZN (INVX0) 0.09 7.01 r

add_100/U2/Q (OR2X1) 0.16 7.17 r

add_100/U53/QN (NAND2X0) 0.49 7.66 f

add_100/U39/QN (NAND2X0) 0.13 7.79 r

add_100/U37/QN (NAND2X0) 0.50 8.29 f

add_100/U34/QN (NAND2X0) 0.12 8.41 r

add_100/U31/QN (NAND2X0) 0.26 8.67 f

add_100/U22/QN (NAND2X0) 0.12 8.78 r

add_100/U50/QN (NAND2X0) 0.22 9.00 f

add_100/U48/QN (NAND2X0) 0.13 9.13 r

add_100/U49/QN (NAND2X0) 0.35 9.48 f

add_100/U46/QN (NAND2X0) 0.12 9.60 r

add_100/U35/Q (XOR2X2) 0.22 9.82 r

add_100/SUM[15] (plus_pipe_DW01_add_5) 0.00 9.82 r

s1_pre3_reg_15_/D (DFFARX1) 0.03 9.86 r

data arrival time 9.86

clock CLK_IN (rise edge) 10.00 10.00

clock network delay (ideal) 0.00 10.00

s1_pre3_reg_15_/CLK (DFFARX1) 0.00 10.00 r

library setup time -0.13 9.87

data required time 9.87

--------------------------------------------------------------------------

data required time 9.87

data arrival time -9.86

--------------------------------------------------------------------------

slack (MET) 0.01

1

check_timing.rpt

Information: Updating design information... (UID-85)

Information: Checking generated_clocks...

Information: Checking loops...

Information: Checking no_input_delay...

Information: Checking unconstrained_endpoints...

Information: Checking pulse_clock_cell_type...

Information: Checking no_driving_cell...

Information: Checking partial_input_delay...

1

area.rpt

****************************************

Report : area

Design : plus_pipe

Version: K-2015.06

Date : Sun Aug 30 15:10:51 2020

****************************************

Library(s) Used:

saed90nm_max_hth (File: /home/XXX/fab/synopsys90nm_lib/stdcel/db/ss1p08v125c/saed90nm_max_hth.db)

Number of ports: 407

Number of nets: 1102

Number of cells: 729

Number of combinational cells: 365

Number of sequential cells: 360

Number of macros/black boxes: 0

Number of buf/inv: 192

Number of references: 7

Combinational area: 3626.495977

Buf/Inv area: 1127.116819

Noncombinational area: 11483.136185

Macro/Black Box area: 0.000000

Net Interconnect area: 614.463091

Total cell area: 15109.632162

Total area: 15724.095253

1

智能推荐

什么是内部类?成员内部类、静态内部类、局部内部类和匿名内部类的区别及作用?_成员内部类和局部内部类的区别-程序员宅基地

文章浏览阅读3.4k次,点赞8次,收藏42次。一、什么是内部类?or 内部类的概念内部类是定义在另一个类中的类;下面类TestB是类TestA的内部类。即内部类对象引用了实例化该内部对象的外围类对象。public class TestA{ class TestB {}}二、 为什么需要内部类?or 内部类有什么作用?1、 内部类方法可以访问该类定义所在的作用域中的数据,包括私有数据。2、内部类可以对同一个包中的其他类隐藏起来。3、 当想要定义一个回调函数且不想编写大量代码时,使用匿名内部类比较便捷。三、 内部类的分类成员内部_成员内部类和局部内部类的区别

分布式系统_分布式系统运维工具-程序员宅基地

文章浏览阅读118次。分布式系统要求拆分分布式思想的实质搭配要求分布式系统要求按照某些特定的规则将项目进行拆分。如果将一个项目的所有模板功能都写到一起,当某个模块出现问题时将直接导致整个服务器出现问题。拆分按照业务拆分为不同的服务器,有效的降低系统架构的耦合性在业务拆分的基础上可按照代码层级进行拆分(view、controller、service、pojo)分布式思想的实质分布式思想的实质是为了系统的..._分布式系统运维工具

用Exce分析l数据极简入门_exce l趋势分析数据量-程序员宅基地

文章浏览阅读174次。1.数据源准备2.数据处理step1:数据表处理应用函数:①VLOOKUP函数; ② CONCATENATE函数终表:step2:数据透视表统计分析(1) 透视表汇总不同渠道用户数, 金额(2)透视表汇总不同日期购买用户数,金额(3)透视表汇总不同用户购买订单数,金额step3:讲第二步结果可视化, 比如, 柱形图(1)不同渠道用户数, 金额(2)不同日期..._exce l趋势分析数据量

宁盾堡垒机双因素认证方案_horizon宁盾双因素配置-程序员宅基地

文章浏览阅读3.3k次。堡垒机可以为企业实现服务器、网络设备、数据库、安全设备等的集中管控和安全可靠运行,帮助IT运维人员提高工作效率。通俗来说,就是用来控制哪些人可以登录哪些资产(事先防范和事中控制),以及录像记录登录资产后做了什么事情(事后溯源)。由于堡垒机内部保存着企业所有的设备资产和权限关系,是企业内部信息安全的重要一环。但目前出现的以下问题产生了很大安全隐患:密码设置过于简单,容易被暴力破解;为方便记忆,设置统一的密码,一旦单点被破,极易引发全面危机。在单一的静态密码验证机制下,登录密码是堡垒机安全的唯一_horizon宁盾双因素配置

谷歌浏览器安装(Win、Linux、离线安装)_chrome linux debian离线安装依赖-程序员宅基地

文章浏览阅读7.7k次,点赞4次,收藏16次。Chrome作为一款挺不错的浏览器,其有着诸多的优良特性,并且支持跨平台。其支持(Windows、Linux、Mac OS X、BSD、Android),在绝大多数情况下,其的安装都很简单,但有时会由于网络原因,无法安装,所以在这里总结下Chrome的安装。Windows下的安装:在线安装:离线安装:Linux下的安装:在线安装:离线安装:..._chrome linux debian离线安装依赖

烤仔TVの尚书房 | 逃离北上广?不如押宝越南“北上广”-程序员宅基地

文章浏览阅读153次。中国发达城市榜单每天都在刷新,但无非是北上广轮流坐庄。北京拥有最顶尖的文化资源,上海是“摩登”的国际化大都市,广州是活力四射的千年商都。GDP和发展潜力是衡量城市的数字指...

随便推点

java spark的使用和配置_使用java调用spark注册进去的程序-程序员宅基地

文章浏览阅读3.3k次。前言spark在java使用比较少,多是scala的用法,我这里介绍一下我在项目中使用的代码配置详细算法的使用请点击我主页列表查看版本jar版本说明spark3.0.1scala2.12这个版本注意和spark版本对应,只是为了引jar包springboot版本2.3.2.RELEASEmaven<!-- spark --> <dependency> <gro_使用java调用spark注册进去的程序

汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用_uds协议栈 源代码-程序员宅基地

文章浏览阅读4.8k次。汽车零部件开发工具巨头V公司全套bootloader中UDS协议栈源代码,自己完成底层外设驱动开发后,集成即可使用,代码精简高效,大厂出品有量产保证。:139800617636213023darcy169_uds协议栈 源代码

AUTOSAR基础篇之OS(下)_autosar 定义了 5 种多核支持类型-程序员宅基地

文章浏览阅读4.6k次,点赞20次,收藏148次。AUTOSAR基础篇之OS(下)前言首先,请问大家几个小小的问题,你清楚:你知道多核OS在什么场景下使用吗?多核系统OS又是如何协同启动或者关闭的呢?AUTOSAR OS存在哪些功能安全等方面的要求呢?多核OS之间的启动关闭与单核相比又存在哪些异同呢?。。。。。。今天,我们来一起探索并回答这些问题。为了便于大家理解,以下是本文的主题大纲:[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JCXrdI0k-1636287756923)(https://gite_autosar 定义了 5 种多核支持类型

VS报错无法打开自己写的头文件_vs2013打不开自己定义的头文件-程序员宅基地

文章浏览阅读2.2k次,点赞6次,收藏14次。原因:自己写的头文件没有被加入到方案的包含目录中去,无法被检索到,也就无法打开。将自己写的头文件都放入header files。然后在VS界面上,右键方案名,点击属性。将自己头文件夹的目录添加进去。_vs2013打不开自己定义的头文件

【Redis】Redis基础命令集详解_redis命令-程序员宅基地

文章浏览阅读3.3w次,点赞80次,收藏342次。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。此时,可以将系统中所有用户的 Session 数据全部保存到 Redis 中,用户在提交新的请求后,系统先从Redis 中查找相应的Session 数据,如果存在,则再进行相关操作,否则跳转到登录页面。当数据量很大时,count 的数量的指定可能会不起作用,Redis 会自动调整每次的遍历数目。_redis命令

URP渲染管线简介-程序员宅基地

文章浏览阅读449次,点赞3次,收藏3次。URP的设计目标是在保持高性能的同时,提供更多的渲染功能和自定义选项。与普通项目相比,会多出Presets文件夹,里面包含着一些设置,包括本色,声音,法线,贴图等设置。全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,主光源和附加光源在一次Pass中可以一起着色。URP:全局只有主光源和附加光源,主光源只支持平行光,附加光源数量有限制,一次Pass可以计算多个光源。可编程渲染管线:渲染策略是可以供程序员定制的,可以定制的有:光照计算和光源,深度测试,摄像机光照烘焙,后期处理策略等等。_urp渲染管线