Verilog CIC 滤波器设计(代码自取)_cic截止频率-程序员宅基地

前言:积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器,资源消耗少,运算速率高,可实现高速滤波,常用在输入采样率最高的第一级,在多速率信号处理系统中具有着广泛应用。

1. DDC 原理

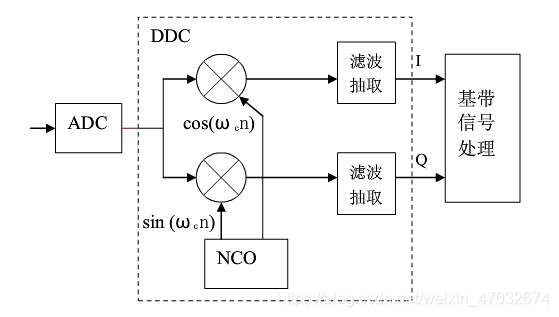

DDC 主要由本地振荡器(NCO) 、混频器、滤波器等组成,如下图所示。

DDC 将中频信号与振荡器产生的载波信号进行混频,信号中心频率被搬移,再经过抽取滤波,恢复原始信号,实现了下变频功能。

中频数据采样时,需要很高的采样频率来确保 ADC(模数转换器)采集到信号的信噪比。经过数字下变频后,得到的基带信号采样频率仍然是 ADC 采样频率,所以数据率很高。此时基带信号的有效带宽往往已经远小于采样频率,所以利用抽取、滤波进行数据速率的转换,使采样率降低,避免资源的浪费和设计的困难,就成为 DDC 不可缺少的一部分。

而采用 CIC 滤波器进行数据处理,是 DDC 抽取滤波部分最常用的方法。

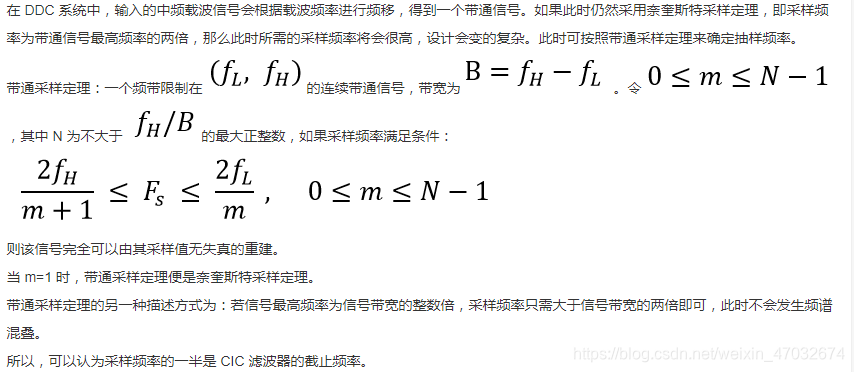

2.带通采样定理

3. DDC 频谱搬移

例如一个带宽信号中心频率为 60MHz,带宽为 8MHz, 则频率范围为 56MHz ~ 64MHz,m 的可取值范围为 0 ~ 7。取 m=1, 则采样频率范围为 64MHz ~ 112MHz。

取采样频率为 80MHz,设 NCO 中心频率为 20 MHz,下面讨论复信号频谱搬移示意图。

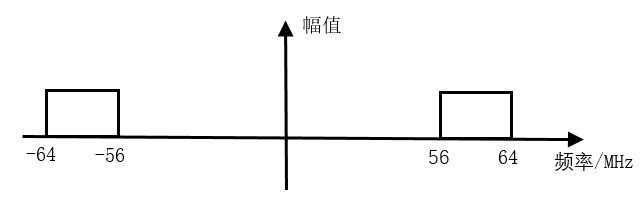

(1)考虑频谱的对称性,输入复信号的频谱示意图如下:

(2)80MHz 采样频率采样后,56~64MHz 的频带被搬移到了 -24~ -16MHz 与 136 ~ 144MHz(高于采样频率被滤除)的频带处,-64~ -56MHz 的频带被搬移到 -144~ -136MHz(高于采样频率被滤除)与 16~24MHz 的频带处。

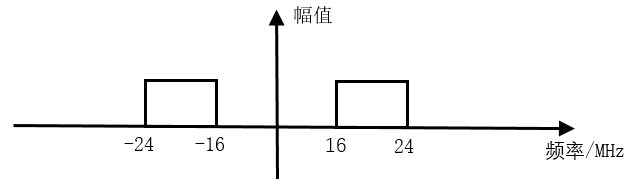

采样后频带分布如下:

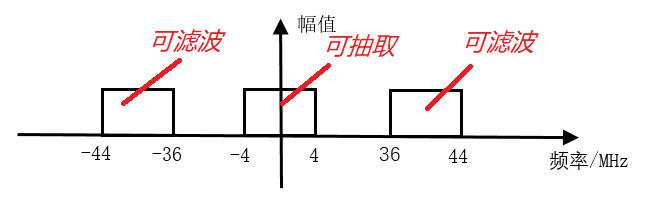

(3)信号经过 20MHz NCO 的正交电路后, -24~ -16MHz 的频带被搬移到 -4~4MHz 与 -44~ -36MHz 的频带处,16~24MHz 的频带被搬移到 -4~4MHz 与 36~44MHz 的频带处,如下所示。

(4)此时中频输入的信号已经被搬移到零中频基带处。

-44~ -36MHz 和 36~44MHz 的带宽信号是不需要的,可以滤除;-4~4MHz 的零中频信号数据速率仍然是 80MHz,可以进行抽取降低数据速率。而 CIC 滤波,就是要完成这个过程。

上述复习了很多数字信号处理的内容,权当抛 DDC 的砖,引 CIC 的玉。

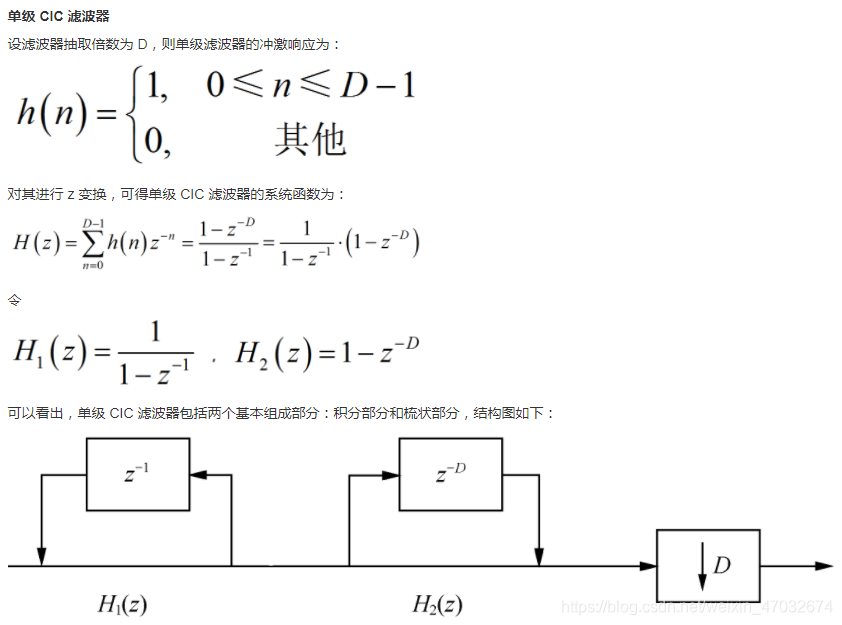

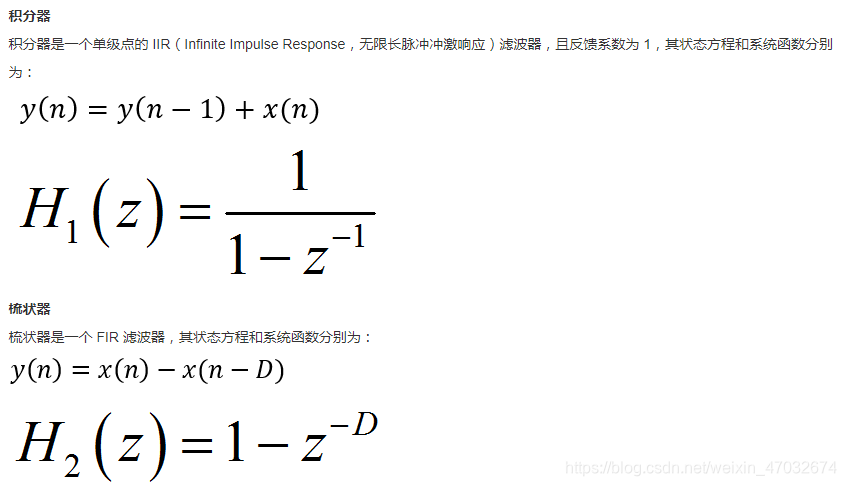

4.CIC 滤波器原理

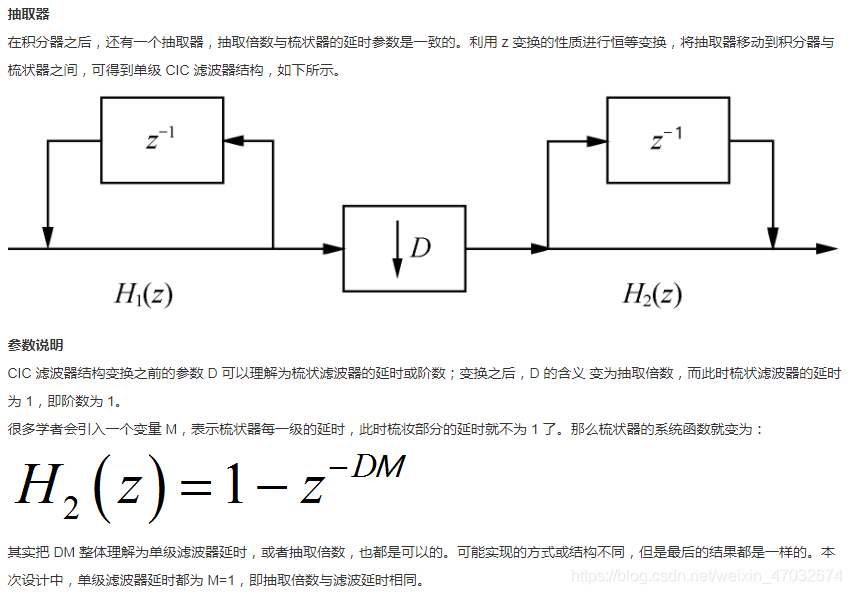

多级 CIC 滤波器

单级 CIC 滤波器的阻带衰减较差,为了提高滤波效果,抽取滤波时往往会采用多级 CIC 滤波器级联的结构。

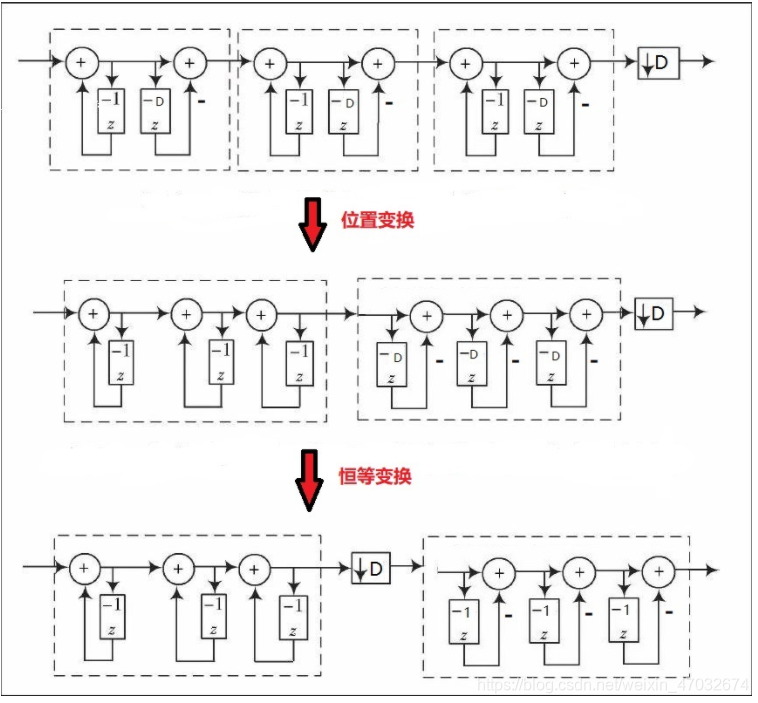

实现多级直接级联的 CIC 滤波器在设计和资源上并不是最优的方式,需要对其结构进行调整。如下所示,将积分器和梳状滤波器分别移至一组,并将抽取器移到梳状滤波器之前。先抽取再进行滤波,可以减少数据处理的长度,节约硬件资源。

当然,级联数越大,旁瓣抑制越好,但是通带内的平坦度也会变差。所以级联数不宜过多,一般最多 5 级。

5.CIC 滤波器设计

设计说明

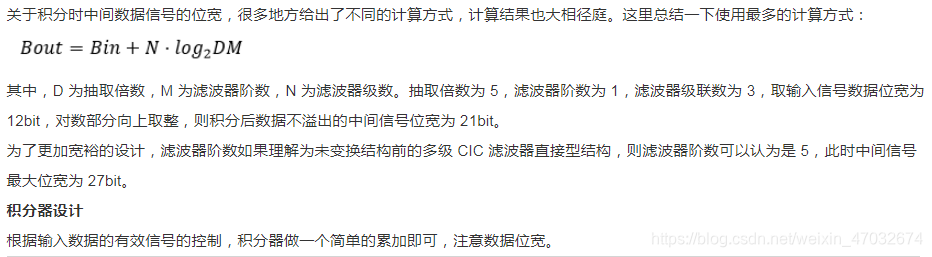

CIC 滤波器本质上就是一个简单的低通滤波器,截止频率为采样频率除以抽取倍数后的一半。输入数据信号仍然是 7.5MHz 和 250KHz,采样频率 50MHz。抽取倍数设置为 5,则截止频率为 5MHz,小于 7.5MHz,可以滤除 7.5MHz 的频率成分。设计参数如下:

输入频率: 7.5MHz 和 250KHz

采样频率: 50MHz

阻带: 5MHz

阶数: 1(M=1)

级数: 3(N=3)

//3 stages integrator

module integrator

#(parameter NIN = 12,

parameter NOUT = 21)

(

input clk ,

input rstn ,

input en ,

input [NIN-1:0] din ,

output valid ,

output [NOUT-1:0] dout) ;

reg [NOUT-1:0] int_d0 ;

reg [NOUT-1:0] int_d1 ;

reg [NOUT-1:0] int_d2 ;

wire [NOUT-1:0] sxtx = {

{(NOUT-NIN){1'b0}}, din} ;

//data input enable delay

reg [2:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else begin

en_r <= {en_r[1:0], en};

end

end

//integrator

//stage1

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d0 <= 'b0 ;

end

else if (en) begin

int_d0 <= int_d0 + sxtx ;

end

end

//stage2

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d1 <= 'b0 ;

end

else if (en_r[0]) begin

int_d1 <= int_d1 + int_d0 ;

end

end

//stage3

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d2 <= 'b0 ;

end

else if (en_r[1]) begin

int_d2 <= int_d2 + int_d1 ;

end

end

assign dout = int_d2 ;

assign valid = en_r[2];

endmodule

抽取器设计

抽取器设计时,对积分器输出的数据进行计数,然后间隔 5 个数据进行抽取即可。

module decimation

#(parameter NDEC = 21)

(

input clk,

input rstn,

input en,

input [NDEC-1:0] din,

output valid,

output [NDEC-1:0] dout);

reg valid_r ;

reg [2:0] cnt ;

reg [NDEC-1:0] dout_r ;

//counter

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 3'b0;

end

else if (en) begin

if (cnt==4) begin

cnt <= 'b0 ;

end

else begin

cnt <= cnt + 1'b1 ;

end

end

end

//data, valid

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

valid_r <= 1'b0 ;

dout_r <= 'b0 ;

end

else if (en) begin

if (cnt==4) begin

valid_r <= 1'b1 ;

dout_r <= din;

end

else begin

valid_r <= 1'b0 ;

end

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

梳状器设计

梳状滤波器就是简单的一阶 FIR 滤波器,每一级的 FIR 滤波器对数据进行一个时钟延时,然后做相减即可。因为系数为 ±1,所以不需要乘法器。

module comb

#(parameter NIN = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

//en delay

reg [5:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else if (en) begin

en_r <= {en_r[5:0], en} ;

end

end

reg [NOUT-1:0] d1, d1_d, d2, d2_d, d3, d3_d ;

//stage 1, as fir filter, shift and add(sub),

//no need for multiplier

always @(posedge clk or negedge rstn) begin

if (!rstn) d1 <= 'b0 ;

else if (en) d1 <= din ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d1_d <= 'b0 ;

else if (en) d1_d <= d1 ;

end

wire [NOUT-1:0] s1_out = d1 - d1_d ;

//stage 2

always @(posedge clk or negedge rstn) begin

if (!rstn) d2 <= 'b0 ;

else if (en) d2 <= s1_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d2_d <= 'b0 ;

else if (en) d2_d <= d2 ;

end

wire [NOUT-1:0] s2_out = d2 - d2_d ;

//stage 3

always @(posedge clk or negedge rstn) begin

if (!rstn) d3 <= 'b0 ;

else if (en) d3 <= s2_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d3_d <= 'b0 ;

else if (en) d3_d <= d3 ;

end

wire [NOUT-1:0] s3_out = d3 - d3_d ;

//tap the output data for better display

reg [NOUT-1:0] dout_r ;

reg valid_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

dout_r <= 'b0 ;

valid_r <= 'b0 ;

end

else if (en) begin

dout_r <= s3_out ;

valid_r <= 1'b1 ;

end

else begin

valid_r <= 1'b0 ;

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

顶层例化

按信号的流向将积分器、抽取器、梳状器分别例化,即可组成最后的 CIC 滤波器模块。

梳状滤波器的最终输出位宽一般会比输入信号小一些,这里取 17bit。当然输出位宽完全可以与输入数据的位宽一致。

module cic

#(parameter NIN = 12,

parameter NMAX = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

wire [NMAX-1:0] itg_out ;

wire [NMAX-1:0] dec_out ;

wire [1:0] en_r ;

integrator #(.NIN(NIN), .NOUT(NMAX))

u_integrator (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (en_r[0]),

.dout (itg_out));

decimation #(.NDEC(NMAX))

u_decimator (

.clk (clk),

.rstn (rstn),

.en (en_r[0]),

.din (itg_out),

.dout (dec_out),

.valid (en_r[1]));

comb #(.NIN(NMAX), .NOUT(NOUT))

u_comb (

.clk (clk),

.rstn (rstn),

.en (en_r[1]),

.din (dec_out),

.valid (valid),

.dout (dout));

endmodule

testbench

testbench 编写如下,主要功能就是不间断连续的输入 250KHz 与 7.5MHz 的正弦波混合信号数据。输入的混合信号数据也可由 matlab 生成,具体过程参考《并行 FIR 滤波器设计》一节。

module test ;

parameter NIN = 12 ;

parameter NMAX = 21 ;

parameter NOUT = NMAX ;

reg clk ;

reg rstn ;

reg en ;

reg [NIN-1:0] din ;

wire valid ;

wire [NOUT-1:0] dout ;

//=====================================

// 50MHz clk generating

localparam T50M_HALF = 10000;

initial begin

clk = 1'b0 ;

forever begin

# T50M_HALF clk = ~clk ;

end

end

//============================

// reset and finish

initial begin

rstn = 1'b0 ;

# 30 ;

rstn = 1'b1 ;

# (T50M_HALF * 2 * 2000) ;

$finish ;

end

//=======================================

// read cos data into register

parameter SIN_DATA_NUM = 200 ;

reg [NIN-1:0] stimulus [0: SIN_DATA_NUM-1] ;

integer i ;

initial begin

$readmemh("../tb/cosx0p25m7p5m12bit.txt", stimulus) ;

i = 0 ;

en = 0 ;

din = 0 ;

# 200 ;

forever begin

@(negedge clk) begin

en = 1 ;

din = stimulus[i] ;

if (i == SIN_DATA_NUM-1) begin

i = 0 ;

end

else begin

i = i + 1 ;

end

end

end

end

cic #(.NIN(NIN), .NMAX(NMAX), .NOUT(NOUT))

u_cic (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (valid),

.dout (dout));

endmodule // test

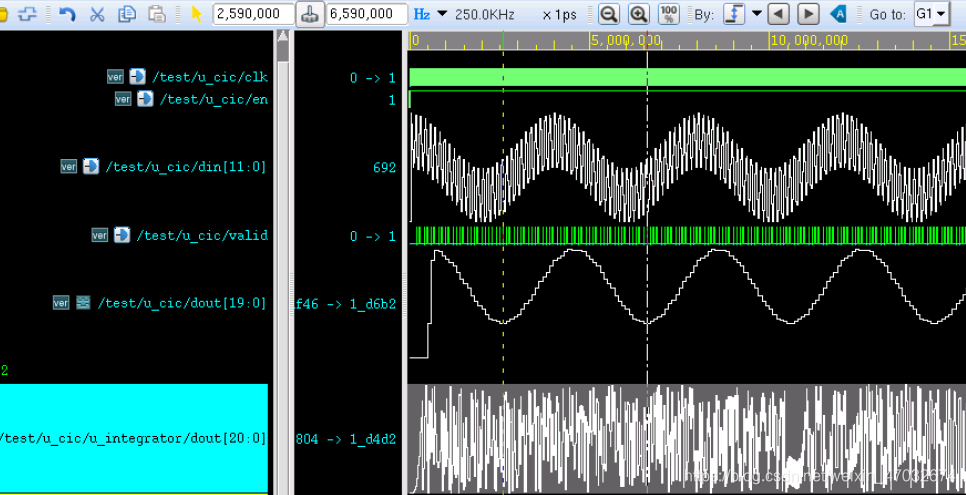

6.仿真结果

由下图仿真结果可知,经过 CIC 滤波器后的信号只有一种低频率信号(250KHz),高频信号(7.5MHz)被滤除了。

但是波形不是非常完美,这与设计的截止频率、数据不是持续输出等有一定关系。

此时发现,积分器输出的数据信号也非常的不规则,这与其位宽有关系。

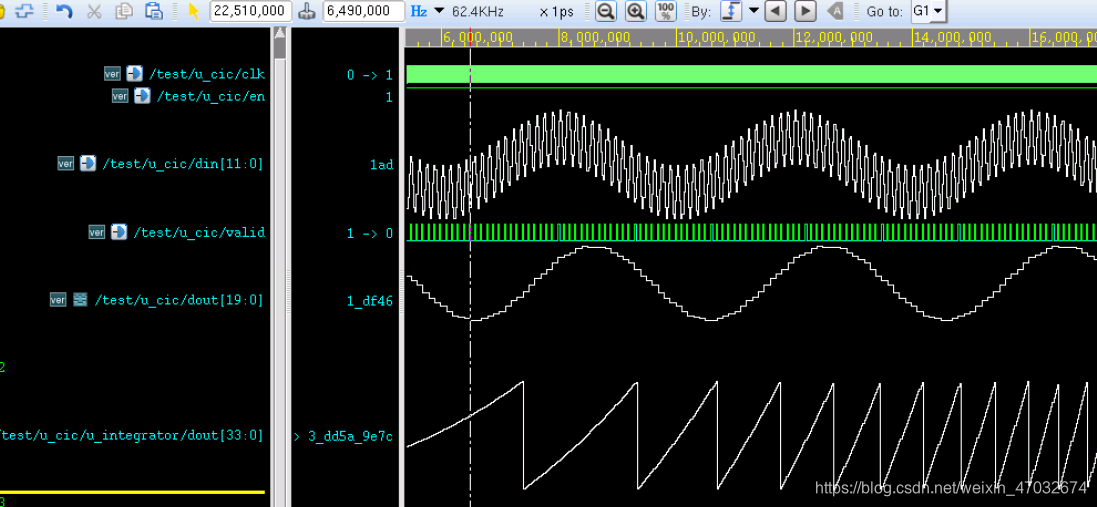

为了更好的观察积分器输出的数据,将其位宽由 21bit 改为 34bit,仿真结果如下。

此时发现,CIC 滤波器的数据输出并没有实质性的变化,但是积分器输出的数据信号呈现锯齿状,也称之为梳状。这也是梳状滤波器名字的由来。

智能推荐

从零开始搭建Hadoop_创建一个hadoop项目-程序员宅基地

文章浏览阅读331次。第一部分:准备工作1 安装虚拟机2 安装centos73 安装JDK以上三步是准备工作,至此已经完成一台已安装JDK的主机第二部分:准备3台虚拟机以下所有工作最好都在root权限下操作1 克隆上面已经有一台虚拟机了,现在对master进行克隆,克隆出另外2台子机;1.1 进行克隆21.2 下一步1.3 下一步1.4 下一步1.5 根据子机需要,命名和安装路径1.6 ..._创建一个hadoop项目

心脏滴血漏洞HeartBleed CVE-2014-0160深入代码层面的分析_heartbleed代码分析-程序员宅基地

文章浏览阅读1.7k次。心脏滴血漏洞HeartBleed CVE-2014-0160 是由heartbeat功能引入的,本文从深入码层面的分析该漏洞产生的原因_heartbleed代码分析

java读取ofd文档内容_ofd电子文档内容分析工具(分析文档、签章和证书)-程序员宅基地

文章浏览阅读1.4k次。前言ofd是国家文档标准,其对标的文档格式是pdf。ofd文档是容器格式文件,ofd其实就是压缩包。将ofd文件后缀改为.zip,解压后可看到文件包含的内容。ofd文件分析工具下载:点我下载。ofd文件解压后,可以看到如下内容: 对于xml文件,可以用文本工具查看。但是对于印章文件(Seal.esl)、签名文件(SignedValue.dat)就无法查看其内容了。本人开发一款ofd内容查看器,..._signedvalue.dat

基于FPGA的数据采集系统(一)_基于fpga的信息采集-程序员宅基地

文章浏览阅读1.8w次,点赞29次,收藏313次。整体系统设计本设计主要是对ADC和DAC的使用,主要实现功能流程为:首先通过串口向FPGA发送控制信号,控制DAC芯片tlv5618进行DA装换,转换的数据存在ROM中,转换开始时读取ROM中数据进行读取转换。其次用按键控制adc128s052进行模数转换100次,模数转换数据存储到FIFO中,再从FIFO中读取数据通过串口输出显示在pc上。其整体系统框图如下:图1:FPGA数据采集系统框图从图中可以看出,该系统主要包括9个模块:串口接收模块、按键消抖模块、按键控制模块、ROM模块、D.._基于fpga的信息采集

微服务 spring cloud zuul com.netflix.zuul.exception.ZuulException GENERAL-程序员宅基地

文章浏览阅读2.5w次。1.背景错误信息:-- [http-nio-9904-exec-5] o.s.c.n.z.filters.post.SendErrorFilter : Error during filteringcom.netflix.zuul.exception.ZuulException: Forwarding error at org.springframework.cloud..._com.netflix.zuul.exception.zuulexception

邻接矩阵-建立图-程序员宅基地

文章浏览阅读358次。1.介绍图的相关概念 图是由顶点的有穷非空集和一个描述顶点之间关系-边(或者弧)的集合组成。通常,图中的数据元素被称为顶点,顶点间的关系用边表示,图通常用字母G表示,图的顶点通常用字母V表示,所以图可以定义为: G=(V,E)其中,V(G)是图中顶点的有穷非空集合,E(G)是V(G)中顶点的边的有穷集合1.1 无向图:图中任意两个顶点构成的边是没有方向的1.2 有向图:图中..._给定一个邻接矩阵未必能够造出一个图

随便推点

MDT2012部署系列之11 WDS安装与配置-程序员宅基地

文章浏览阅读321次。(十二)、WDS服务器安装通过前面的测试我们会发现,每次安装的时候需要加域光盘映像,这是一个比较麻烦的事情,试想一个上万个的公司,你天天带着一个光盘与光驱去给别人装系统,这将是一个多么痛苦的事情啊,有什么方法可以解决这个问题了?答案是肯定的,下面我们就来简单说一下。WDS服务器,它是Windows自带的一个免费的基于系统本身角色的一个功能,它主要提供一种简单、安全的通过网络快速、远程将Window..._doc server2012上通过wds+mdt无人值守部署win11系统.doc

python--xlrd/xlwt/xlutils_xlutils模块可以读xlsx吗-程序员宅基地

文章浏览阅读219次。python–xlrd/xlwt/xlutilsxlrd只能读取,不能改,支持 xlsx和xls 格式xlwt只能改,不能读xlwt只能保存为.xls格式xlutils能将xlrd.Book转为xlwt.Workbook,从而得以在现有xls的基础上修改数据,并创建一个新的xls,实现修改xlrd打开文件import xlrdexcel=xlrd.open_workbook('E:/test.xlsx') 返回值为xlrd.book.Book对象,不能修改获取sheett_xlutils模块可以读xlsx吗

关于新版本selenium定位元素报错:‘WebDriver‘ object has no attribute ‘find_element_by_id‘等问题_unresolved attribute reference 'find_element_by_id-程序员宅基地

文章浏览阅读8.2w次,点赞267次,收藏656次。运行Selenium出现'WebDriver' object has no attribute 'find_element_by_id'或AttributeError: 'WebDriver' object has no attribute 'find_element_by_xpath'等定位元素代码错误,是因为selenium更新到了新的版本,以前的一些语法经过改动。..............._unresolved attribute reference 'find_element_by_id' for class 'webdriver

DOM对象转换成jQuery对象转换与子页面获取父页面DOM对象-程序员宅基地

文章浏览阅读198次。一:模态窗口//父页面JSwindow.showModalDialog(ifrmehref, window, 'dialogWidth:550px;dialogHeight:150px;help:no;resizable:no;status:no');//子页面获取父页面DOM对象//window.showModalDialog的DOM对象var v=parentWin..._jquery获取父window下的dom对象

什么是算法?-程序员宅基地

文章浏览阅读1.7w次,点赞15次,收藏129次。算法(algorithm)是解决一系列问题的清晰指令,也就是,能对一定规范的输入,在有限的时间内获得所要求的输出。 简单来说,算法就是解决一个问题的具体方法和步骤。算法是程序的灵 魂。二、算法的特征1.可行性 算法中执行的任何计算步骤都可以分解为基本可执行的操作步,即每个计算步都可以在有限时间里完成(也称之为有效性) 算法的每一步都要有确切的意义,不能有二义性。例如“增加x的值”,并没有说增加多少,计算机就无法执行明确的运算。 _算法

【网络安全】网络安全的标准和规范_网络安全标准规范-程序员宅基地

文章浏览阅读1.5k次,点赞18次,收藏26次。网络安全的标准和规范是网络安全领域的重要组成部分。它们为网络安全提供了技术依据,规定了网络安全的技术要求和操作方式,帮助我们构建安全的网络环境。下面,我们将详细介绍一些主要的网络安全标准和规范,以及它们在实际操作中的应用。_网络安全标准规范