Quartus使用步骤及联合Modelsim仿真教程_quartus仿真-程序员宅基地

#使用记录#

对于Quartus的安装步骤这里不再进行讲解,modelsim的安装步骤后续文章会进行讲解,这里也就不过多说明。言归正传,现在来开始我们的使用教程:

一、工程创建

1、首先点击打开Quartus软件,博主这里使用的是22版本的,其他版本的步骤也基本一样。

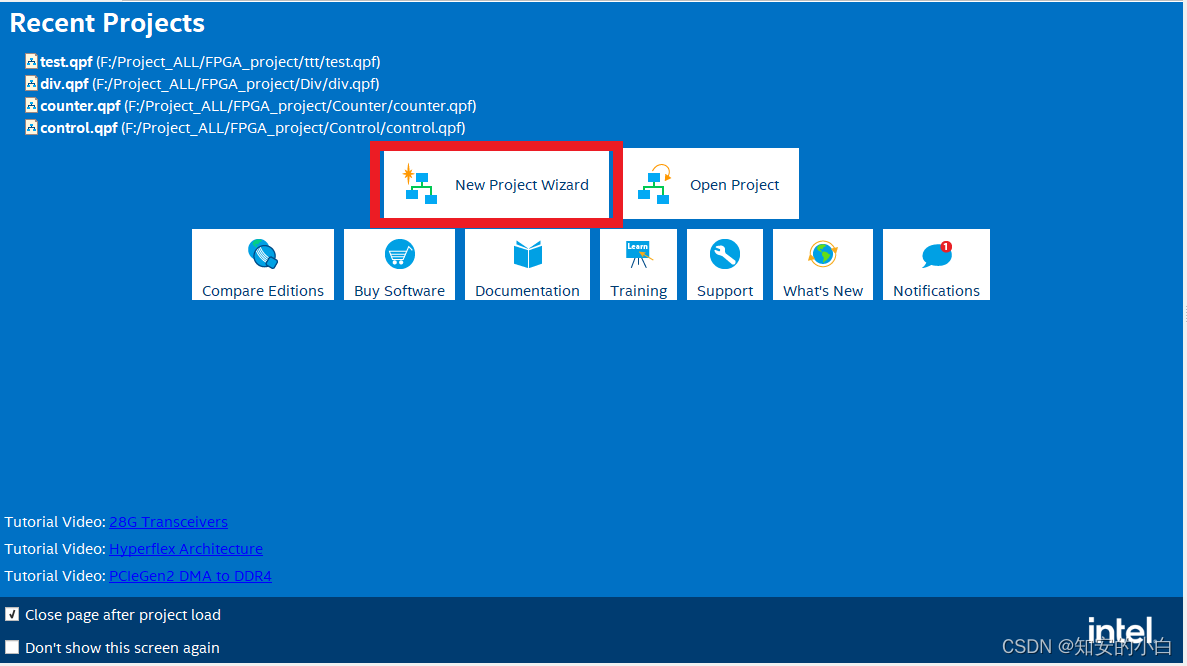

2、我们可以看到如下界面,点击新建工程

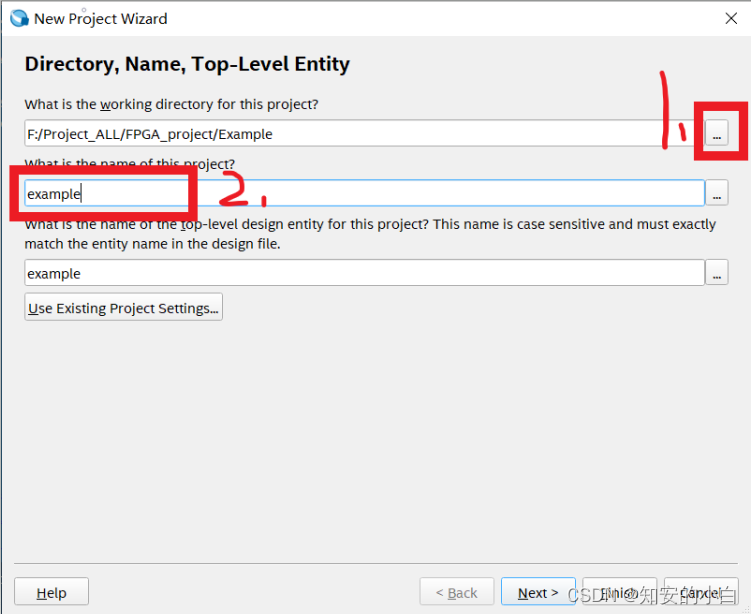

3、首先点击浏览,选择工程文件存放位置,然后修改工程名称,然后点击下方NEXT继续下一步

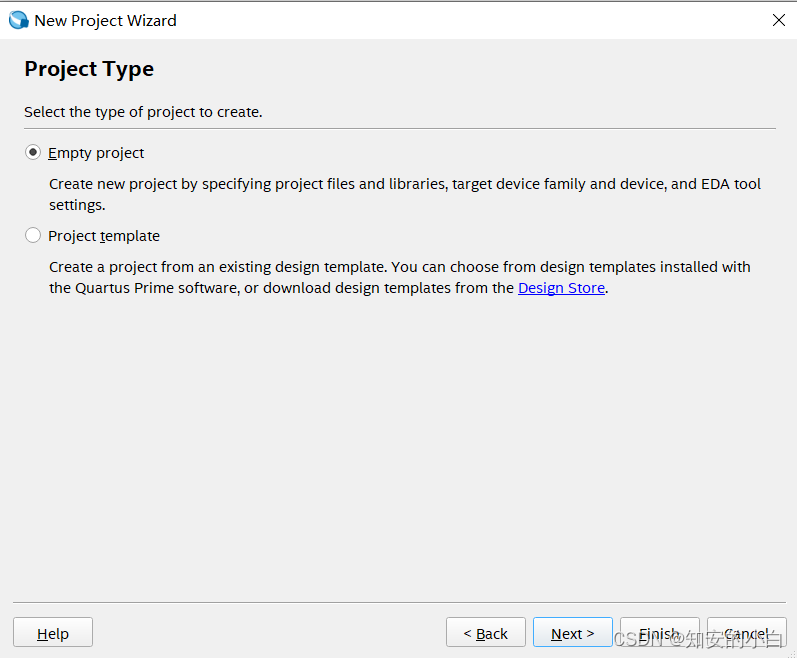

4、这不用管它直接默认选择空工程,然后点击NEXT

5、这里是添加文件,因为我们没有需要添加的,所以也不需要管,点击NEXT进入下一步就行

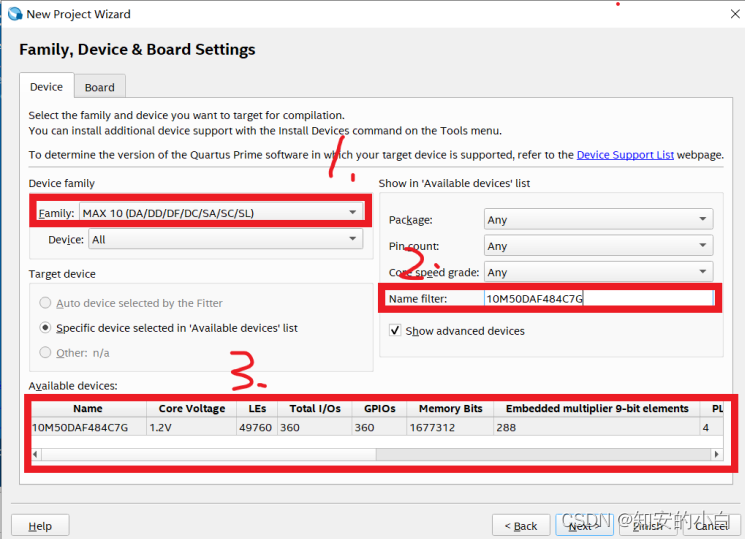

6、这里首先点击选择你需要的芯片的芯片包,然后再输入对应的芯片,最后在下面即可看到芯片,然后点击NEXT进入下一步

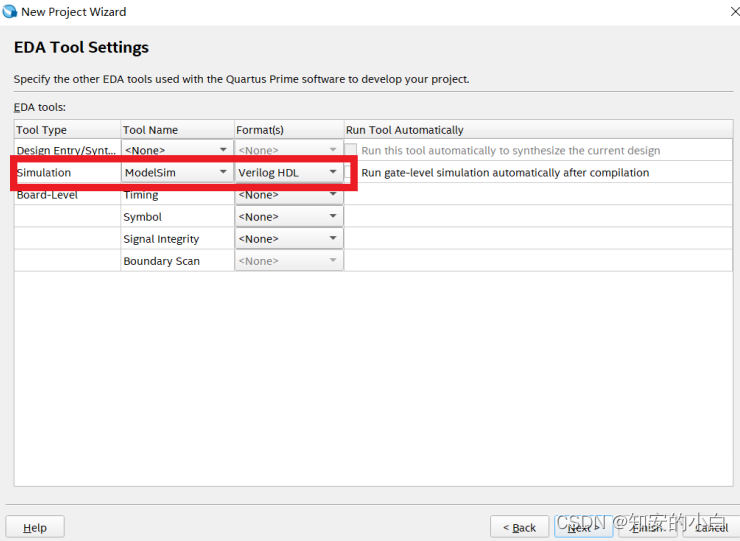

7、这里点击选择仿真方式以及编写程序使用的语言,选择完成点击NEXT进入下一步

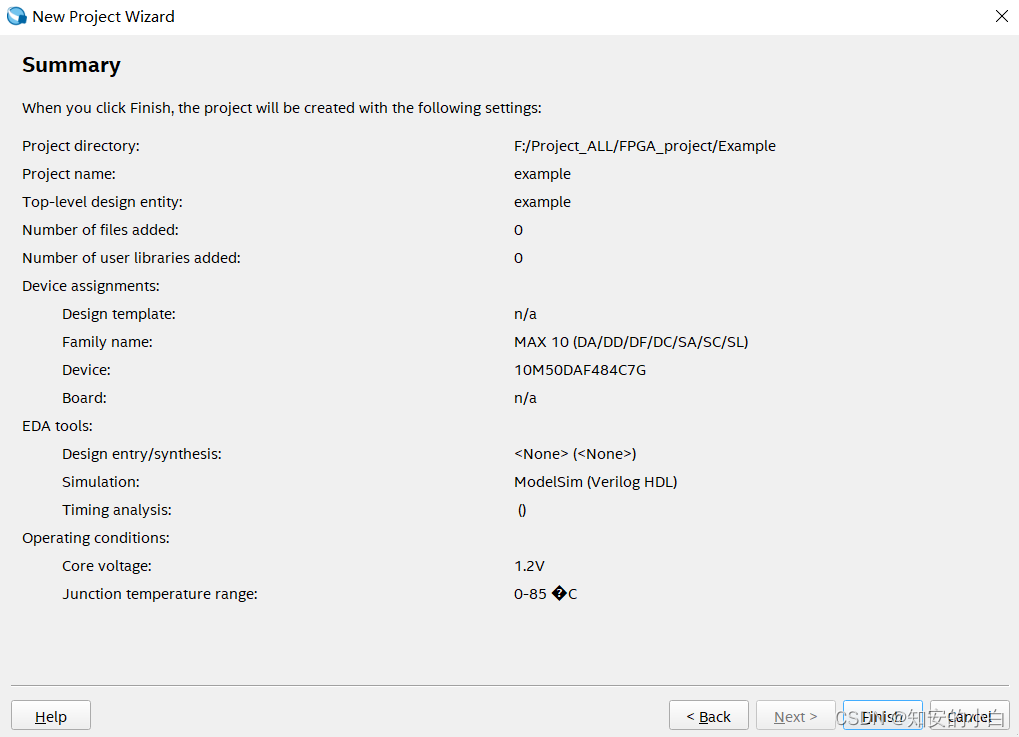

8、点击Finish,工程创建就完成了

二、简单代码编写及下载

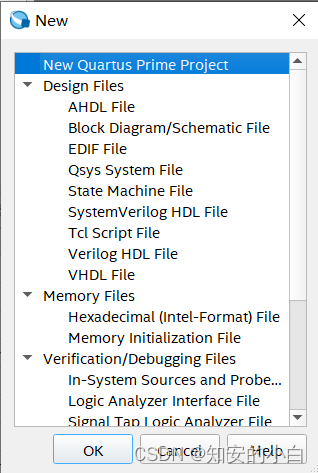

1、点击左上角File-->New新建,出现如下界面,选择你的文件类型,原理图输入就选择Block Diagram/Schematic File,我们这里使用代码输入,并且是Verilog HDL语言,所以选择Verilog HDL File然后点击OK。

2、再出现的界面输入代码,这里是一个测试代码,可以复制使用:

module example(

input clk,

input rst_n,

input data,

output pos_edge, //上升沿

output neg_edge, //下降沿

output data_edge, //数据边沿

output reg [1:0] D

);

//设置两个寄存器,实现前后电平状态的寄存

//相当于对dat_i 打两拍

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

D <= 2'b00;

end

else begin

D <= {D[0], data}; //D[1]表示前一状态,D[0]表示后一状态(新数据)

end

end

//组合逻辑进行边沿检测

assign pos_edge = ~D[1] & D[0];

assign neg_edge = D[1] & ~D[0];

assign data_edge = pos_edge | neg_edge;

endmodule

3、点击如下按钮编译程序

4、出现如下界面,点击Yes保存文件

5、这里保存的名字和前面的module名称一样,否则会报错

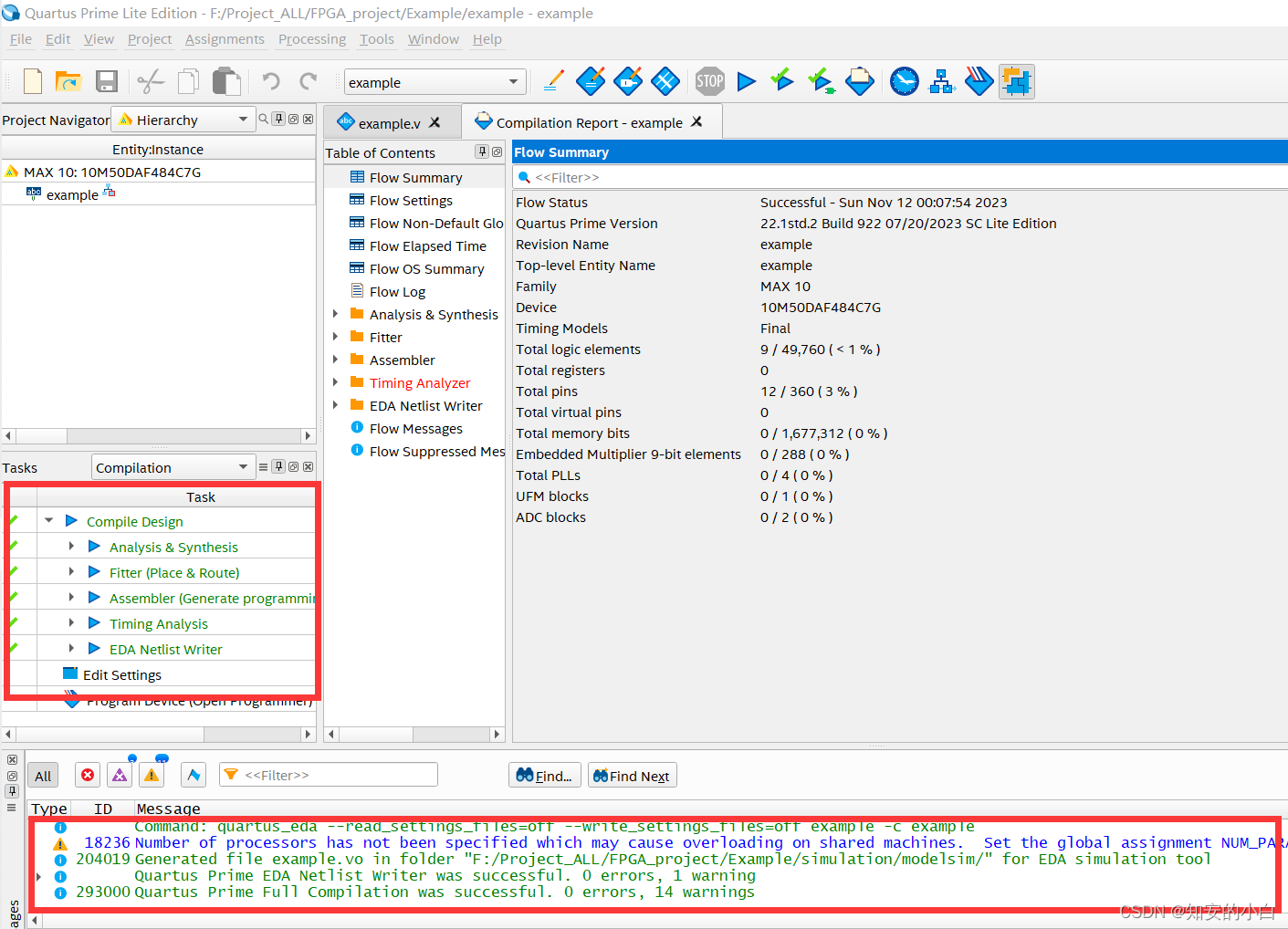

6、看到如下结果就是编译正常,没有问题

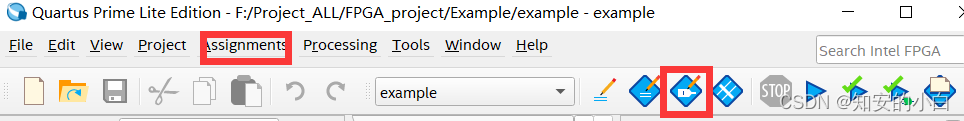

7、然后是绑定引脚,有两种方式可以点击上方Assignments再选择Pin Planner或者点击如图右边的按钮进行绑定,绑定结束再进行一次编译,没有出问题接下来就是下载程序到开发板

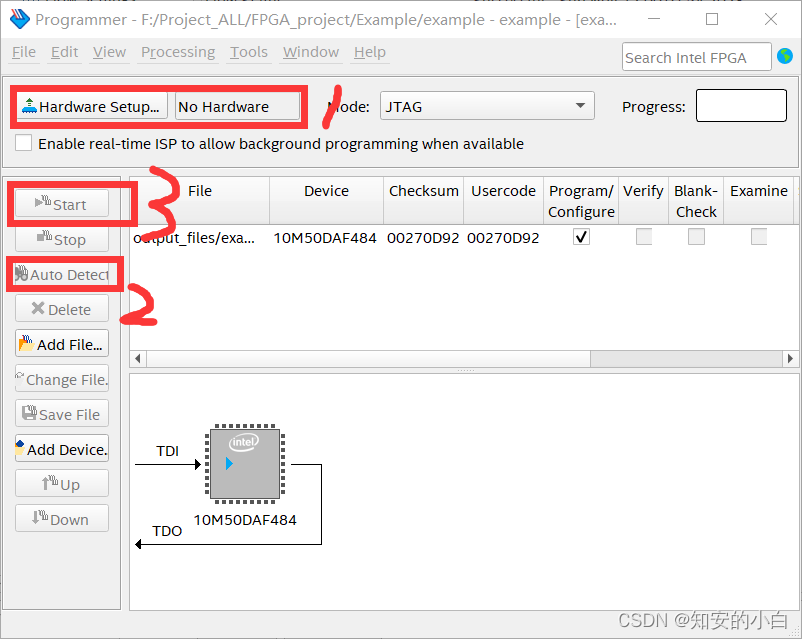

8、选择Tools下面的programmer,或者下图按钮

9、先点击下图1位置选择硬件连接,然后点击Auto Detect进行自动检测,做后点击Start等待上方Progress下载完成即可在开发板看到对应效果。

三、与Modelsim进行联合仿真

1、点击Processing-->Start-->Start test bench template writer,这时我们的文件夹之下已经有了一个example.vt文件

2、对刚才生成的文件进行修改(可以直接复制下面代码,注意名称),然后在编译一次

`timescale 1ns/1ns

module example_tb;

reg clk;

reg rst_n;

reg data;

wire pos_edge;

wire neg_edge;

wire data_edge;

wire [1:0] D;

example u1(

.clk(clk),

.rst_n(rst_n),

.data(data),

.pos_edge(pos_edge),

.neg_edge(neg_edge),

.data_edge(data_edge),

.D(D)

);

//产生时钟激励

initial clk = 1;

always #10 clk = ~clk;

//输入激励

initial begin

rst_n=0;

data=0;

#100;

rst_n = 1;

#50

data=1;

#201;

data=0;

#201;

data=1;

#101;

data=0;

#200;

$stop;

end

endmodule

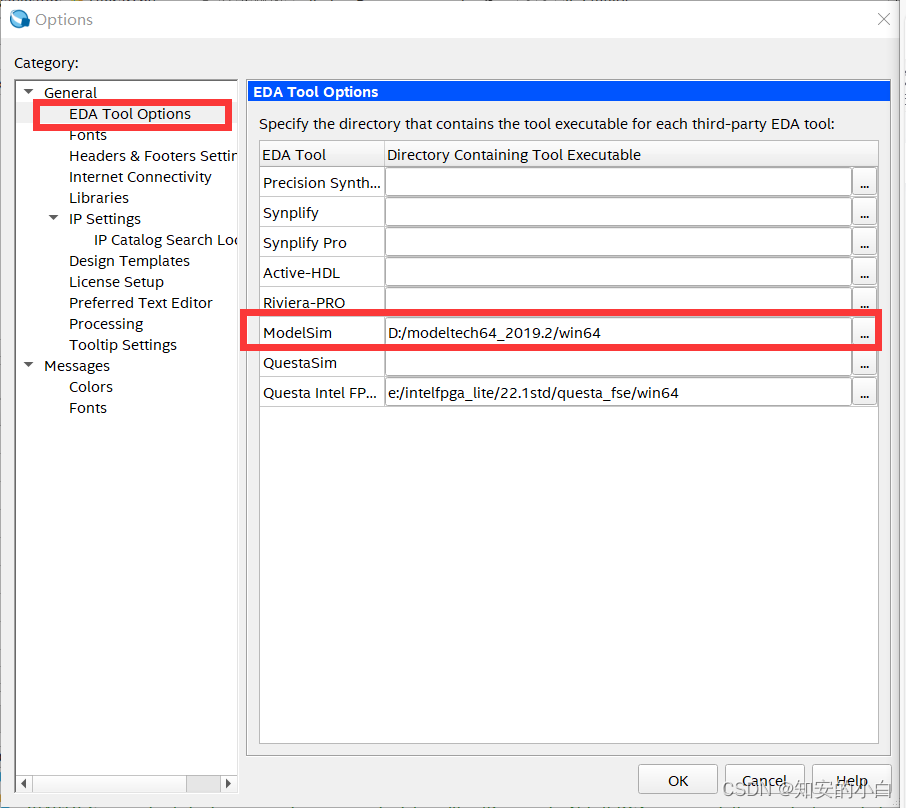

3、现在设置仿真,点击Tools-->Options-->EDA ToolsOptions选项,点击浏览Modelsim安装目录下的Win64或者Win32

4、然后对仿真文件设置点击Assignments-->Settings,再点击下面的Simulation按照如图设置

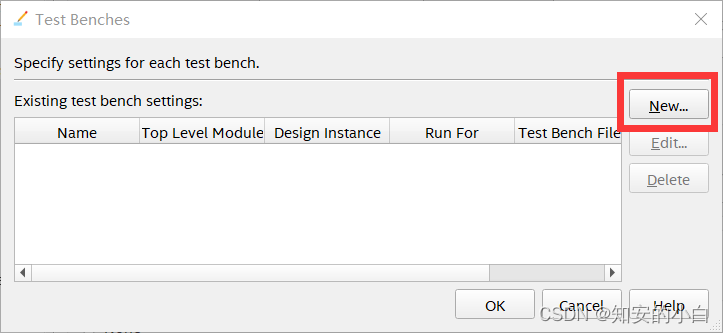

5、选择上面的Compile test bench点击后面Test Bench进入选择,点击New新建

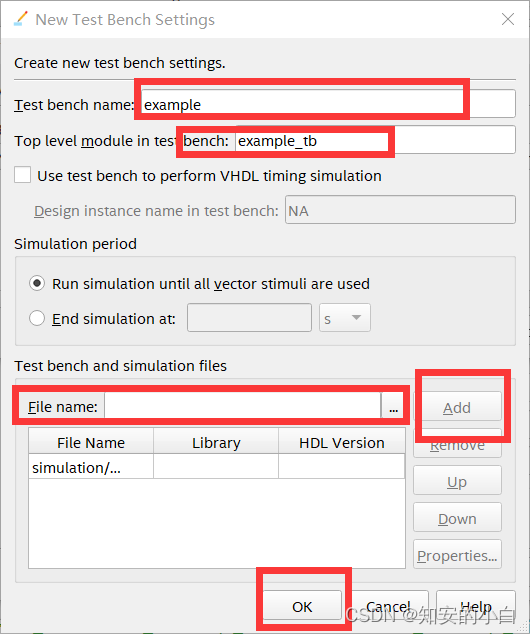

6、按照顺序先编辑名字,然后浏览刚才的.vt文件,最后点击Add添加达到如下图效果,再点击OK,这里如果浏览的是.vo文件则后面仿真需要自己设置时间及电平,然后一直点击OK回到代码编辑界面

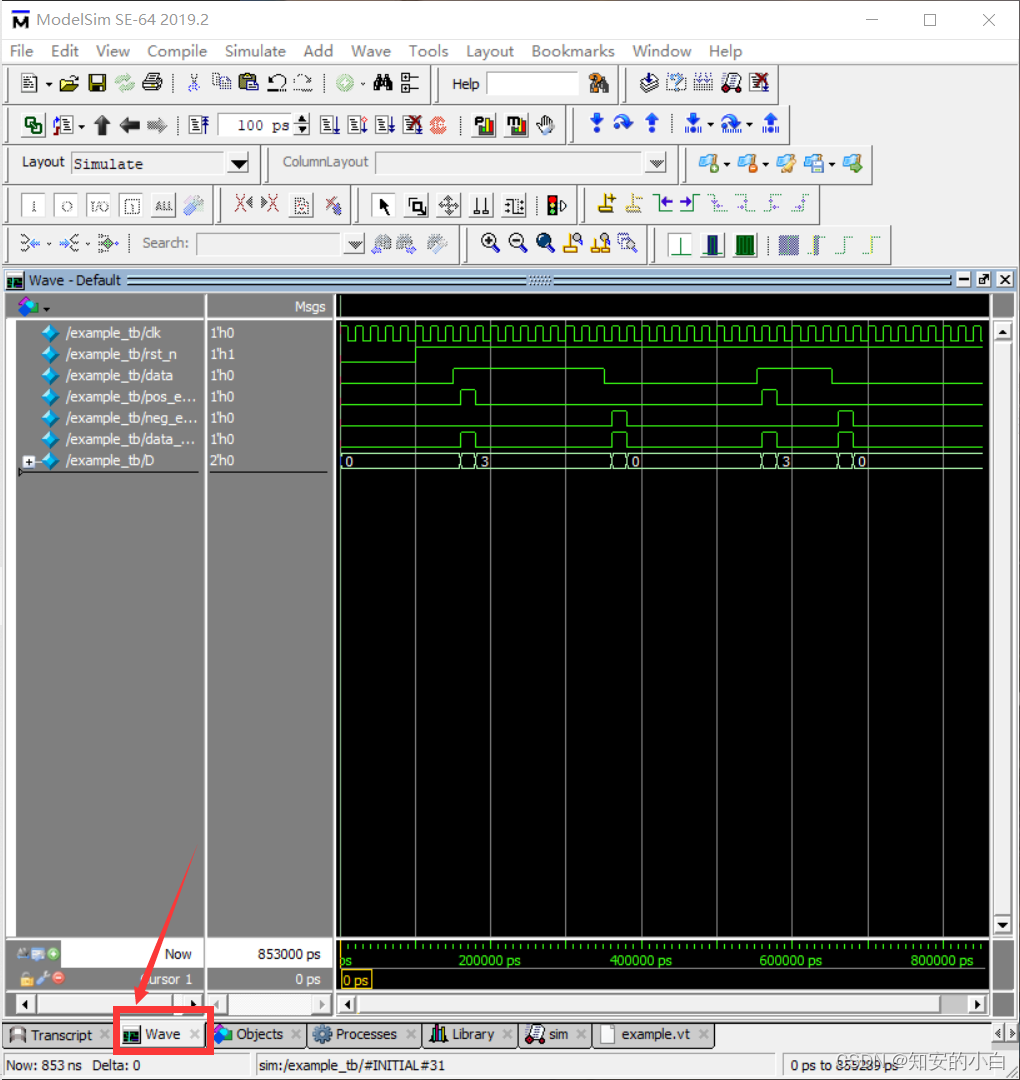

7、点击如下图按钮,然后点击仿真,会自动跳转Modelsim

8、选择下面的Wave即可看到波形,到这里就结束了

写在最后,希望文章可以帮到初学者,文章有不对的地方欢迎指出来一起学习,一起进步。

智能推荐

攻防世界_难度8_happy_puzzle_攻防世界困难模式攻略图文-程序员宅基地

文章浏览阅读645次。这个肯定是末尾的IDAT了,因为IDAT必须要满了才会开始一下个IDAT,这个明显就是末尾的IDAT了。,对应下面的create_head()代码。,对应下面的create_tail()代码。不要考虑爆破,我已经试了一下,太多情况了。题目来源:UNCTF。_攻防世界困难模式攻略图文

达梦数据库的导出(备份)、导入_达梦数据库导入导出-程序员宅基地

文章浏览阅读2.9k次,点赞3次,收藏10次。偶尔会用到,记录、分享。1. 数据库导出1.1 切换到dmdba用户su - dmdba1.2 进入达梦数据库安装路径的bin目录,执行导库操作 导出语句:./dexp cwy_init/[email protected]:5236 file=cwy_init.dmp log=cwy_init_exp.log 注释: cwy_init/init_123..._达梦数据库导入导出

js引入kindeditor富文本编辑器的使用_kindeditor.js-程序员宅基地

文章浏览阅读1.9k次。1. 在官网上下载KindEditor文件,可以删掉不需要要到的jsp,asp,asp.net和php文件夹。接着把文件夹放到项目文件目录下。2. 修改html文件,在页面引入js文件:<script type="text/javascript" src="./kindeditor/kindeditor-all.js"></script><script type="text/javascript" src="./kindeditor/lang/zh-CN.js"_kindeditor.js

STM32学习过程记录11——基于STM32G431CBU6硬件SPI+DMA的高效WS2812B控制方法-程序员宅基地

文章浏览阅读2.3k次,点赞6次,收藏14次。SPI的详情简介不必赘述。假设我们通过SPI发送0xAA,我们的数据线就会变为10101010,通过修改不同的内容,即可修改SPI中0和1的持续时间。比如0xF0即为前半周期为高电平,后半周期为低电平的状态。在SPI的通信模式中,CPHA配置会影响该实验,下图展示了不同采样位置的SPI时序图[1]。CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出。_stm32g431cbu6

计算机网络-数据链路层_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输-程序员宅基地

文章浏览阅读1.2k次,点赞2次,收藏8次。数据链路层习题自测问题1.数据链路(即逻辑链路)与链路(即物理链路)有何区别?“电路接通了”与”数据链路接通了”的区别何在?2.数据链路层中的链路控制包括哪些功能?试讨论数据链路层做成可靠的链路层有哪些优点和缺点。3.网络适配器的作用是什么?网络适配器工作在哪一层?4.数据链路层的三个基本问题(帧定界、透明传输和差错检测)为什么都必须加以解决?5.如果在数据链路层不进行帧定界,会发生什么问题?6.PPP协议的主要特点是什么?为什么PPP不使用帧的编号?PPP适用于什么情况?为什么PPP协议不_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输

软件测试工程师移民加拿大_无证移民,未受过软件工程师的教育(第1部分)-程序员宅基地

文章浏览阅读587次。软件测试工程师移民加拿大 无证移民,未受过软件工程师的教育(第1部分) (Undocumented Immigrant With No Education to Software Engineer(Part 1))Before I start, I want you to please bear with me on the way I write, I have very little gen...

随便推点

Thinkpad X250 secure boot failed 启动失败问题解决_安装完系统提示secureboot failure-程序员宅基地

文章浏览阅读304次。Thinkpad X250笔记本电脑,装的是FreeBSD,进入BIOS修改虚拟化配置(其后可能是误设置了安全开机),保存退出后系统无法启动,显示:secure boot failed ,把自己惊出一身冷汗,因为这台笔记本刚好还没开始做备份.....根据错误提示,到bios里面去找相关配置,在Security里面找到了Secure Boot选项,发现果然被设置为Enabled,将其修改为Disabled ,再开机,终于正常启动了。_安装完系统提示secureboot failure

C++如何做字符串分割(5种方法)_c++ 字符串分割-程序员宅基地

文章浏览阅读10w+次,点赞93次,收藏352次。1、用strtok函数进行字符串分割原型: char *strtok(char *str, const char *delim);功能:分解字符串为一组字符串。参数说明:str为要分解的字符串,delim为分隔符字符串。返回值:从str开头开始的一个个被分割的串。当没有被分割的串时则返回NULL。其它:strtok函数线程不安全,可以使用strtok_r替代。示例://借助strtok实现split#include <string.h>#include <stdio.h&_c++ 字符串分割

2013第四届蓝桥杯 C/C++本科A组 真题答案解析_2013年第四届c a组蓝桥杯省赛真题解答-程序员宅基地

文章浏览阅读2.3k次。1 .高斯日记 大数学家高斯有个好习惯:无论如何都要记日记。他的日记有个与众不同的地方,他从不注明年月日,而是用一个整数代替,比如:4210后来人们知道,那个整数就是日期,它表示那一天是高斯出生后的第几天。这或许也是个好习惯,它时时刻刻提醒着主人:日子又过去一天,还有多少时光可以用于浪费呢?高斯出生于:1777年4月30日。在高斯发现的一个重要定理的日记_2013年第四届c a组蓝桥杯省赛真题解答

基于供需算法优化的核极限学习机(KELM)分类算法-程序员宅基地

文章浏览阅读851次,点赞17次,收藏22次。摘要:本文利用供需算法对核极限学习机(KELM)进行优化,并用于分类。

metasploitable2渗透测试_metasploitable2怎么进入-程序员宅基地

文章浏览阅读1.1k次。一、系统弱密码登录1、在kali上执行命令行telnet 192.168.26.1292、Login和password都输入msfadmin3、登录成功,进入系统4、测试如下:二、MySQL弱密码登录:1、在kali上执行mysql –h 192.168.26.129 –u root2、登录成功,进入MySQL系统3、测试效果:三、PostgreSQL弱密码登录1、在Kali上执行psql -h 192.168.26.129 –U post..._metasploitable2怎么进入

Python学习之路:从入门到精通的指南_python人工智能开发从入门到精通pdf-程序员宅基地

文章浏览阅读257次。本文将为初学者提供Python学习的详细指南,从Python的历史、基础语法和数据类型到面向对象编程、模块和库的使用。通过本文,您将能够掌握Python编程的核心概念,为今后的编程学习和实践打下坚实基础。_python人工智能开发从入门到精通pdf